Накапливающий сумматор

Накапливающий сумматор (НС) обычно представляет собой совокупность сумматора комбинационного типа и регистра (который хранит результаты суммирования как текущие, так и окончательные). Работает такой сумматор по формуле Si = Si-1 + A, ( формула 1.1) где

Si –текущая сумма,

Si-1 –предыдущая(на предыдущем цикле суммирования),

А – очередное текущее слагаемое.

Результат замещает старое значение суммы. Очередное прибавление слагаемого тактируется синхроимпульсами. Учитывая такие особенности функцио-нирования накапливающие сумматоры называются иногда аккумуляторами. На схемах сумматоры обозначаются SM. В российских сериях интегральных микросхем(ИМС), соответственно – ИР(например-К155ИМ3). В американских

сериях они отдельно не обозначаются: SN40S08N. Интегральные микросхемы содержат,как правило, четырехразрядные комбинационные сумматоры. Чаще всего применяют четырехразрядные сумматоры комбинационного типа. Помимо выходных разрядов суммы и выхода переноса в сумматорах предусмотрен вход расширения С для обьединения сумматоров с целью повышения разрядности.

Многоразрядные сумматоры можно построить, прибегнув к обьединению синхронизирующих входов, а также соединению соответствующих входов и выходов переноса нескольких базовых сумматоров.

Накапливающие сумматоры применяются также, например, для формирования адреса ОЗУ, в генераторах сигналов произвольной формы.

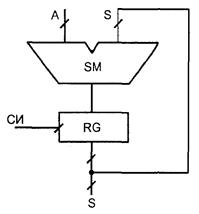

На основании формулы 1.1, описывающе по сути алгоритм работы НС можно предложить структурную схему, приведенную на рис 1.1. Схема работает следующим образом: Перед началом суммирования регистр устанавливается в нулевое состояние по входу R. После поступления слов в сумматор происходит обработка результата, то есть проверяется перенос и происходит собственно суммирование. С выходов сумматора результат суммы поступает на регистр (РГ), который служит для хранения информации и задержки сигнала на один такт. Естественно, сигналы через него будут проходить в том случае, если открыт вход синхронизации. Затем с выходов регистра сигналы поступают в качестве второго слагаемого(20-ти разрядного) на сумматор. Такой цикл повторяется до тех пор, пока не прекратится подача последовательности кодов либо сумма не превысит разрядность 20 (в этом случае сумматор сбрасывается в 0(см. документ Э1)).

Рис 1.1 Структурная схема накапливающего сумматора

Вернуться в оглавление:Цифровые автоматы

Накапливающий сумматор

Накапливающий сумматор обычно представляет собою сочетание комбинационного сумматора и регистра, работающее по формуле S := S + А, согласно которой к содержимому сумматора добавляется очередное слагаемое, и результат замещает старое значение суммы. Структура накапливающего сумматора показана на рис. 11. Очередное прибавление слагаемого тактируется синхроимпульсами СИ. Учитывая особенности функционирования, накапливающие сумматоры называют иногда аккумуляторами.

Рис. 11. Структура накапливающего сумматора

В сериях элементов имеются одноразрядные сумматоры, в том числе с дополнительной входной логикой, двухразрядные и четырехразрядные. Примером стандартных ИС сумматоров могут служить микросхемы ИМЗ серии К555, содержащие четырехразрядный сумматор с последовательным переносом и блок переноса (рис. 2.36), которые непосредственно пригодны для составления из них группового сумматора с цепным переносом.

Микросхемы четырехразрядных сумматоров можно также объединять в групповую структуру с межгрупповым параллельным переносом с помощью специальных блоков ускоренного переноса.

Рис. 12. Структура микросхемы К555ИМ3

В некоторых сериях элементов сумматоры отсутствуют. Причиной этого обычно является наличие арифметико-логического устройства (АЛУ), для которого режим суммирования есть один из возможных режимов.

Цифровые (двоичные) компараторы

Цифровой (двоичный) компаратор(устройство сравнения) [от англ. compare – сравнивать] – это КЦУ, определяющее отношения между двумя двоичными словами.

За основные отношения, через которые можно выразить все остальные, обычно берут два – “равно” (=) и “больше” (>), хотя также можно рассматривать и пару “равно” (=) и “меньше” (

Приняв в качестве основных отношения “равно” (=) и “больше” (>), для всех остальных отношений можно записать:

В сериях цифровых элементов обычно имеются компараторы с тремя выходами: “равно”, “больше” и “меньше” (рис. 3.11). Для краткости записей в обозначении выходных функций компаратора указывается только слово А.

Соотношения входных и выходных сигналов (таблица истинности) компаратора представлены в табл. 3.11.

Таблица 3.11

| Сравниваемые данные | Входы наращивания | Выходы | ||||||||||

| A3, B3 | A2, B2 | A1, B1 | A0, B0 | I(A>B) | I(A B | A B3 | × | × | × | × | × | × |

| A3 B2 | × | × | × | × | × | |||||||

| A3=B3 | A2 B1 | × | × | × | × | |||||||

| – » – | A2=B2 | A1 B0 | × | × | × | |||||||

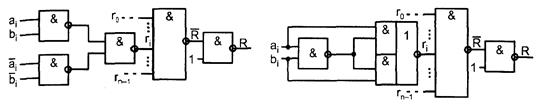

| – » – | – » – | A1=B1 | A0 B, A B), I(A Признак неравенства разрядов Признак равенства двух слов A и B в целом Схема компаратора на равенство в базисе И-НЕ показана на рис. 3.12, а. Рис. 3.12.Схемы компараторов на равенство Схема проверки на равенство без парафазных входов (рис. 3.12, б)основана на выражениях для ri ,преобразованных следующим образом: Построение компаратора на “больше” для одноразрядных слов (табл. 3.12) требует реализации функции запрета по b: Таблица 3.12 Пример реализации компаратора с тремя выходами для двухразрядных слов приведён на рис. 3.13. Выработка признака A > B в этой схеме производится по соотношению (штрихом отмечены функции с выходов младшей группы): Компараторы для слов большой разрядности получают наращиванием размерности путём использования нескольких ИС компараторов. Принцип наращивания хорошо иллюстрируется на том же рис. 3.13. Примером гибкости цифровой схемотехники может служить возможность построения компаратора на равенство с помощью последовательного соединения демультиплексора и мультиплексора, как показано на рис. 3.14. В работе такого компаратора легко разобраться, если вспомнить, как функционируют входящие в него блоки. Пример 3.11. Построить на ЛЭ схему сравнения на равенство двух 8-разрядных чисел. Особенность данной задачи состоит в том, что для её решения практически невозможно построить таблицу: число строк в ней будет 2 (8+8) = Рис. 3.13. Пример построения компаратора Рис. 3.14.Реализация компаратора на равенство Известно, что функция равенства двух аргументов – это инверсия их суммы по модулю 2. Чтобы исключить из проектируемой схемы 8 инверторов воспользуемся соотношением: Решение данной задачи показано на рис. 3.15, б. Оно учитывает, что в семействах ЛЭ нет элемента 8ИЛИ-НЕ, а есть только 4ИЛИ-НЕ. Рис. 3.15. Узел сравнения на равенство 8-разрядных слов Микросхема К555СП1 (рис. 3.16) является 4-разрядным компаратором. Он имеет три выхода: “A>B”, “A ”, ” B), I(A B), I(A=B), I(A B, A=B, A Накапливающий сумматорКомитет Российской Федерации по патентам и товарным знакам (21) 475?261/24 (22) 09.1139 (46) 30.10.93 Бюл. No 39 — 40 (71) Горьковский научно-исследовательский приборостроительный институт (72) Кириллов М.И. (73) Нижегородский научно-исследовательский приборостроительный институт «Кварц» (64) НАКАПЛИВАЮЩИЙ СУММАТОР (57) Изобретение относится к вычислительной технике и может быть использовано в синтезаторах и программируемых генераторах сигналов. Цель изобретения — повышение быстродействия сумматора при сохранении высокой тактовой частоты и (В) RU (11) 20О2297 С1 (51) 5 G06F7 50 возможности наращивания разрядов Накапливающий сумматор содержит выходные регистры и и каскадов, каждый из которых содержит комбинационный сумматор и регистр, а также две группы блоков задержки и переключатель. Повышение быст— родействия достигается тем, что тактовый сигнал на последующий каскад задерживается на величину задержки прохождения сигнала по кольцу каскада накапливающего сумматора. Благодаря этому в этом каскаде успевают сформироваться импульсы переполнения до прихода тактового импульса на следующий каскад и код числа на выходе не искажается даже при высокой тактовой частоте. 2 ил. Изобретение относится к вычислительной технике и может быть использовано в синтезаторах и программируемых генераторах сигналов, Известны накапливающие сумматоры (1), выполненные на основе полных комбинационных сумматоров (a дальнейшем сумматоров) и регистров памяти. На вход сумматора поступает код числа, который складыввется с содержанием регистра памяти. Полученная сумма снова записывается в регистр памяти с каждым тактом входной тактовой последовательности, поступающей по шине ЗАПИСЬ. Эта сумма является слагаемым для последующего прибавляемого числа, При этом параллельный выход сумматоров является выходом суммы, а выход переноса старшего сумматора является выходом старшего разряда этой суммы. Такие накапливающие сумматоры из-за минимального количества входящих элементов имеют высокое быстродействие. Время суммирования включает время срабатывания сумматоров tc и время записи суммы в регистры памяти тз; t g= пт2 + t3, где n — число сумматоров (каскадов). Наиболее близким к заявляемому по технической сущности является накапливающий сумматор (2), содержащий выходные регистры и и каскадов, каждый из которых содержит комбинационный сумматор и регистр, а также тактируемые блоки задержки (регистры), Целью изобретения является увеличение быстродействия при сохранении высокой TBKTQBQA частоты с возможностью наращивания разрядов накапливающего сумматора. Нэ фиг, 1 представлена схема накапливающего сумматора; на фиг. 2 приведены осциллограммы, поясняющие его работу, Накапливающий сумматор содержит п комбинационных сумматоров 1, и регистров 2, 2п-2 блоков 3, 4 задержки первой и второй групп, переключатель 5 и ri выходных регистров 6, Комбинационные сумматоры 1 и регистры 2 образуют каскады 7, Нэкапли5 55 вающий сумматор имеет также информационные входы 8, вход 9 переноса, выход 10 переполнения, информационные выходы 11, вход 12 записи, управляющие входы 13, Подача тактового сигнала на входы каскадов 7 накапливающего сумматора, кроме младшего, осуществляется через блоки 3 задержки, выходной сигнал суммы с каскадов 2. Данилов P.Â. и др. Применение интегральных микросхем в электронной вычислительной технике, Справочник /Под редакцией Б.Н,Файэулаева, Б.В.Табарина. — M. Радио и связь, 1987, с. 114, ф ° Накапливающий сумматорИзобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств отображения информации. Целью изобретения является расширение функциональных возможностей путем обеспечения предварительной записи кода двоичного числа. Поставленная цель достигается тем, что накапливающий сумматор дополнительно содержит счетчик, два элемента НЕ, блок элементов сравнения, триггер, два элемента И с соответствующими связями. 1 ил. 75 1 А1 (19) (111 (51) 5 G 06 F 7/50 Н А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ tlO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ ПРИ ГКНТ СССР (21) 4436807/24-24 (22) 07,06.88 (46) 15.04.90. Бюл, М 14 (72) Н.И.Луканов, А.В.Низовой и К.K ° Костров (53) 681.325 (088,8) (56) Авторское свидетельство СССР 1(- 1251069, кл, G 06 F 7/50, 1985. Справочник по интегральным микросхемам. /Под ред. Б,В.Тарабрина, И.: Энергия, 1981, с. 741, рис.5-250. (54) НАКАПЛИВАЮЩИЙ СУИМАТОР (57) Изобретение относится к автомаИзобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств отображения информации. Цель изобретения — расширение функциональных возможностей накапливающего сумматора путем обеспечения предварительной записи кода двоичного числа. На чертеже изображена структурная схема накапливающего сумматора. Накапливающий сумматор содержит сумматор 1, регистр памяти 2, счетчик 3, первый элемент НЕ 4, блок элементов сравнения 5, второй элемент НЕ 6, триггер 7, первый элемент И 8, второй элемент И 9. 2 тике и вычислительной технике и может быть использовано при построении устройств отображения информации. Целью изобретения является расширение функциональных возможностей путем обеспечения предварительной записи кода двоичного числа. Поставленная цель достигается тем, что накапливающий сумматор дополнительно содержит счетчик, два элемента НЕ, блок элементов сравнения, триггер, два элемента И с соответствующими связями. 1 ил..второй вход элемента И 8 — тактовая частота (Р ); на второй вход блока элементов сравнения 5 — двоичный код числа предварительной записи. Выход счетчика 3 является выходом Д накапливающего сумматора. Накапливающий сумматор работает р следующим образом. Рассмотрим работу схемы с приходом сигнала «Обнуление», под действием которого триггер 7 переключается и © с его выхода на первый вход элемента ©1 Одновременно сигнал «Обнуление» инвертируется элементом НЕ 4, поступает на вход установки нуля R счетчика 3 и обнуляет его. На выходе счетчика 3 по всем разрядам устанавливается значение «0», которое поступает на сумматор 1 и блок. элементов сравнения 5. Значение «0» на выходе счетчика 3 сохраняется в течение действия сигнала Обнуление». С окончанием сигнала «Обнуление» импульсы тактовой частоты Г через элемент И 8 поступают на вход «прямого счета » (+1) реверсивного счетчика Триггер 7 переключается. Прохождение тактовых импульсов через элемент И 8 на счетчик 3 прекращается, так как с переключением триггера 7 с его выхода на первый вход элемента И 8 поступает напряжение «О», Так перед началом суммирования осуществляется запись счетчик 3 кода заданного двоичного числа. Далее на вход сумматора 1 поступа- 5 ет код двоичного числа, который складывается с содержимым счетчика 3. Полученная сумма записывается в регистр памяти 2 в момент спада сигнала «Запись» на его входе С2. Этим же импульсом, но с задержкой на эле30 менте И 9, по потенциалу «О», поступающего на вход предварительной записи С счетчика 3, двоичный код числа из регистра памяти 2 переписывается в счетчик 3. 35 С приходом следующего сигнала «Запись» цикл суммирования повторяется. В результате суммирования на выходе накапливающего сумматора получаем значение двоичного кода S Sиз + в nit где S — значение двоичного кода чисI ла на выходе накапливающего сумматора; S — предварительно записанное п,з число в счетчик перед суммированием; С приходом сигнала «Обнуление» весь цикл повторяется. Формула и з обретения Накапливающий сумматор, содержащий сумматор и регистр памяти, при этом выход сумматора соединен с информационным входом регистра памяти, а второй вход сумматора — с входом суммируемо- го числа накапливающего сумматора, отличающийся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения предварительной записи кода двоичного числа, в накапливающий сумматор введены счетчик, два элемента НЕ, блок элементов сравнения, триггер, два элемента И, при этом выход регистра памяти соединен с информационным входом счетчика, выход которого соединен с первыми входами сумматора и блока элементов сравнения, выход первого элемента НЕ соединен с входом установки нуля счетчика, вход Прямой счет» которого соединен с выходом первого элемента И, первый вход кото« рого соединен с выходом триггера, вход установки в нулевое состояние триггера соединен с выходом второго элемента НЕ, вход которого соединен с выходом блока элементов сравнения, выход второго элемента И соединен с управляющим входом предварительной записи счетчика, вход управления предварительной записи регистра памяти и вход второго элемента И соединены с входом сигнала «Запись» накапливающего сумматора, вход первого элемента НЕ и вход установки в единичное состояние триггера соединены со входом сигнала «Обнуление» накапливающего сумматора, второй вход первого элемента И соединен с входом тактовой частоты накапливающего сумматора, второй вход блока элементов сравнения соединен с входом кода числа предварительной записи накапливающего сумматора, а выход счетчика соединен с выходом накапливающего сумматора. Редактор И.Товтин,Техред Л.Олийнык Корректор Т,Малец ВНИИПИ Государственного комитета по изобретениям и открь:тиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-издательский комбинат «Патент», r ° Ужгород, ул. Гагарина, 101 Одноразрядный накапливающий сумматорОдноразрядным сумматором накапливающего типа является схема, суммирующая поочередно поступающие на ее вход цифры слагаемого и переноса с запоминанием результата суммирования. Для запоминания результата сложения на выходе рассмотренных комбинационных сумматоров можно установить триггеры памяти (триггера R-S и D-типов). Совместно с триггером памяти комбинационный сумматор будет выполнять функции накапливающего сумматора. Роль накапливающего сумматора может выполнять и счетный триггер со схемой формирования переноса, на счетный вход которого все слагаемые должны подаваться последовательно во времени. Суммирование трех слагаемых будет проходить поэтому за три такта. В первый момент времени t1 через схему ИЛИ1 на вход Т-триггера, который был предварительно установлен в нулевое состояние, поступает цифра ai и запоминается. После завершения переходных процессов в триггере в момент времени t2 через схему ИЛИ1 поступает цифра вi второго слагаемого. При этом Т-триггер реализует функцию

Сигнал переноса Pi+1 формируется комбинационной схемой, стоящей на выходе триггера. В момент времени t3, когда триггер еще находится в состоянии f1, приходит сигнал Pi. На выходе И1 имеем

Окончательно, сигнал переноса Pi+1 на выходе ИЛИ2 равен Недостаток рассмотренного сумматора заключается в том, что он имеет малое быстродействие, поскольку в каждом цикле суммирования число срабатываний триггера может равняться четырем (Уст «0», ai(t1), bi(t2), Pi(t3)). Достоинство накапливающего сумматора по сравнению с комбинационным состоит в более простой организации суммирования с накоплением результата, благодаря его способности к запоминанию. Полученная сумма сохраняется в сумматоре и после снятия входных сигналов. Нам важно ваше мнение! Был ли полезен опубликованный материал? Да | Нет |

.

. .

. .

.

.

. .

.

.

.

Отечественной промышленностью выпускаются компараторы ТТЛ 555СП1, 531СП1 и КМОП 561ИП2.

Отечественной промышленностью выпускаются компараторы ТТЛ 555СП1, 531СП1 и КМОП 561ИП2.

. Наконец в следующий момент времени t3 через схему ИЛИ1 подаетсяцифра переноса из более младшего разряда Pi и триггер реализует функцию:

. Наконец в следующий момент времени t3 через схему ИЛИ1 подаетсяцифра переноса из более младшего разряда Pi и триггер реализует функцию:

, которая совпадает с функцией Si, полученной ранее по таблице истинности одноразрядного сумматора. Таким образом, по истечении трех тактов в триггере будет находится значение i-ого разряда суммы слагаемых А и В, т.е. Si.

, которая совпадает с функцией Si, полученной ранее по таблице истинности одноразрядного сумматора. Таким образом, по истечении трех тактов в триггере будет находится значение i-ого разряда суммы слагаемых А и В, т.е. Si. . Если теперь к f3 добавить через дизъюнкцию ai×bi, то получится Pi+1. Непосредственно ai×bi получить с помощью конъюнктора нельзя, т.к. они поступают в различные дискретные моменты времени. Поэтому ai×bi формируются с помощью элемента И2 реализующего функцию

. Если теперь к f3 добавить через дизъюнкцию ai×bi, то получится Pi+1. Непосредственно ai×bi получить с помощью конъюнктора нельзя, т.к. они поступают в различные дискретные моменты времени. Поэтому ai×bi формируются с помощью элемента И2 реализующего функцию .

.