Будущее и настоящее СБИС

Рубрика: Технические науки

Дата публикации: 05.09.2016 2016-09-05

Статья просмотрена: 730 раз

Библиографическое описание:

Чепрасова, А. С. Будущее и настоящее СБИС / А. С. Чепрасова, Ю. В. Мамелин. — Текст : непосредственный // Молодой ученый. — 2016. — № 17 (121). — С. 79-81. — URL: https://moluch.ru/archive/121/33559/ (дата обращения: 09.12.2021).

In the article function and further development of extralarge integral microsystems (EIM) are considered. Classifications and meaning of EIM are taken into account, current technologies of microsystem design are analyzed. Current topic is considered as gadgets become smaller, but their productivity is getting much better than the productivity of their ancestors decade ago. Such gradation is possible only with the technologies mentioned in the article.

Key words: microsystem, degree of integration, programmable logic, architecture, step-and-repeat camera

В настоящее время во многих бытовых, вычислительных и прочих приборах используются интегральные схемы,твердотельные устройства, изготовленные на полупроводниковой подложке (пластине или пленке) и помещенные в неразборный корпус. Такие схемы имеют небольшой размер, но большой функционал. Создание первых полупроводниковых интегральных схем (1958–59) и начало их серийного выпуска (1960–61) определили рождениемикроэлектроники.

В наш век, век высоких технологий, интегральные схемы увеличили свой размер и функционал, и чем дальше, тем все сложнее их проектировать, особенно вручную. Необходимо учесть огромное количество связей и переходов с уровня на уровень, именно поэтому автоматизация проектирования ИС стало неотъемлемой составляющей научно-технического прогресса. Проектирование технических объектовбез автоматизации требует чрезмерно больших временных и людских ресурсов. Проекты наиболеесложных объектов, к которым прежде всего относятсябольшие интегральные схемы(БИС), сверхбольшиеинтегральные схемы(СБИС) и вычислительные системы, создаются с обязательным использованием систем автоматизированного проектирования [1, с. 152].

Надо отметить, что БИС и СБИС составляют подавляющее большинство интегральных микросхем, однако далеко не все. Существует классификация микросхем по степени интеграции.

В СССР были предложены следующие названия микросхем в зависимости от степени интеграции (указано количество элементов для цифровых схем):

‒ Малая интегральная схема (МИС) — до 100 элементов в кристалле.

‒ Средняя интегральная схема (СИС) — до 1000 элементов в кристалле.

‒ Большая интегральная схема (БИС) — до 10000 элементов в кристалле.

‒ Сверхбольшая интегральная схема (СБИС) — до 1 миллиона элементов в кристалле.

‒ Ультрабольшая интегральная схема (УБИС) — до 1 миллиарда элементов в кристалле.

‒ Гигабольшая интегральная схема (ГБИС) — более 1 миллиарда элементов в кристалле [5, электронный ресурс].

В настоящее время название ГБИС практически не используется (например, последние версии процессоров Pentium 4 содержат пока несколько сотен миллионов транзисторов), и все схемы с числом элементов, превышающим 10000, относят к классу СБИС, считая УБИС его подклассом.

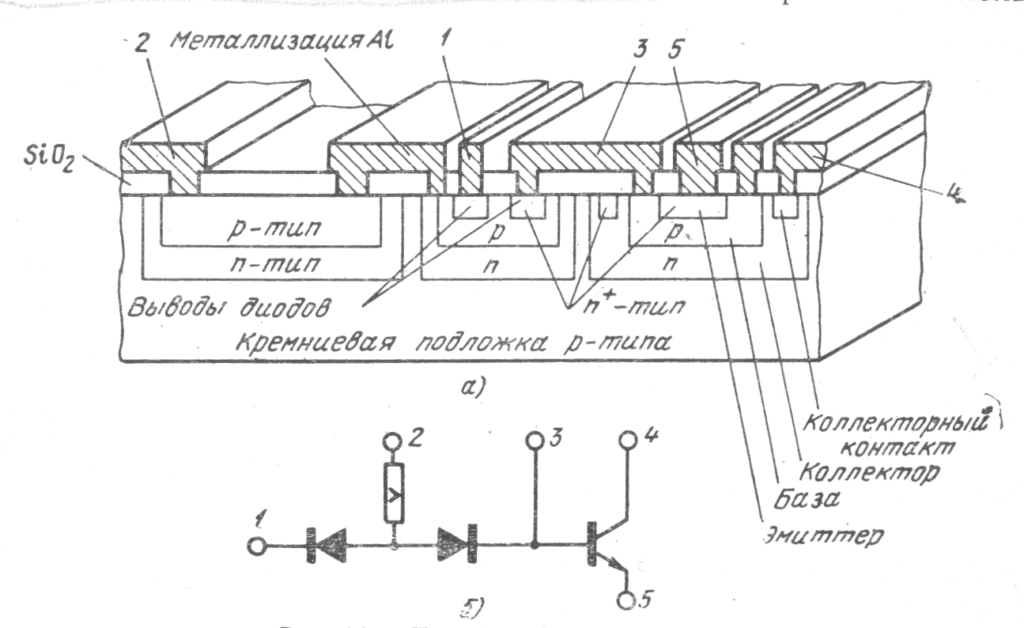

Одним из наиболее используемых элементов СБИС является транзистор на основе структуры металл-диэлектрик-полупроводник (МОП) Первый транзистор, работающий на эффекте поля, был продемонстрирован в 1960 году. Сначала полевые транзисторы с двуокисью кремния в качестве подзатворного диэлектрика формировались на подложке n- типа проводимости. Затем, из-за большей подвижности электронов, чем у дырок при формировании сверхбольших быстродействующих интегральных схем стали использовать n- канальные транзисторы, формируемые на p- подложке.

Отечественным производителям электронной техники трудно конкурировать с зарубежными фирмами в области массового производства товаров широкого потребления. Однако в области разработки и создания сложной наукоемкой продукции в России сохранились условия, кадры, научный потенциал. Большое число предприятий и учреждений способно разрабатывать уникальные электронные устройства. Высокотехнологичным «сырьем» для таких разработок в области цифровой электроники служат легко доступные на отечественном рынке электронные компоненты: контроллеры, микропроцессоры, СБИС памяти и тд. — все, что позволяет решать задачи специальной обработки сигналов и вычислений программным путем. Микропроцессорная техника давно и прочно укоренилась в отечественных разработках. Однако в последние годы появилась новая элементная база — СБИС программируемой логики (СБИС ПЛ), которая удачно дополняя и заменяя микропроцессорные средства, в ближайшие годы станет «настольным материалом» для разработчиков. СБИС ПЛ оказываются вне конкуренции в областях, где требуется создание высокопроизводительных специализированных устройств, ориентированных на аппаратную реализацию. Аппаратное решение задач обеспечивает распараллеливание процесса и увеличивает производительность в десятки раз по сравнению с программным решением, а использование СБИС ПЛ, в отличие от специализированных СБИС, обеспечивает такую же гибкость реализации, как у любых программных решений. В последние годы динамика развития производства СБИС ПЛ уступает только микросхемам памяти и превышает 50 % в год.

Производители, архитектура и возможности существующих в настоящее время типов СБИС ПЛ разнообразны. Систематизация микросхем гибкой логики производится обычно по следующим классификационным признакам:

‒ степень интеграции (логическая емкость);

‒ архитектура функционального преобразователя;

‒ организация внутренней структуры СБИС и структуры матрицы соединений функциональных преобразователей;

‒ тип используемого программируемого элемента;

‒ наличие внутренней оперативной памяти.

Степень интеграции (логическая емкость) — наиболее важная характеристика СБИС ПЛ, по которой осуществляется выбор. Производители СБИС ПЛ стоят на передовых рубежах электронной технологии (текущая рабочая проектная норма составляет 0,25 мкм), и число транзисторов в СБИС ПЛ большой емкости составляет десятки миллионов. Но ввиду избыточности структур, включающих большое число коммутирующих транзисторов, логическую емкость измеряют в эквивалентных логических вентилях типа 2И-НЕ (2ИЛИ-НЕ), которые понадобилось бы для реализации устройств той же сложности, что и на соответствующих СБИС [2, c. 52].

Помимо сложной внутренней организации элементов, сложности их взаимодействия, существует немаловажная часть создания СБИС — физическое изготовление спроектированной конструкции. Для воплощения в жизнь сверхбольшой интегральной микросхемы используется фотопроцесс. Схема формируется на подложке, в большинстве случаев из диоксида кремния, полученного термическим оксидированием кремния. Ввиду малости размера элементов микросхем, от использования видимого света и даже ближнего ультрафиолета при засветке давно отказались. В качестве характеристики технологического процесса производства микросхем указывают ширину полосы фотоповторителя и, как следствие, размеры транзисторов и прочих элементов на кристалле. Однако, этот параметр находится во взаимосвязи с рядом других производственных возможностей: чистотой получаемого кремния, характеристиками инжекторов, методами вытравливания и напыления.

Микросхемы выпускаются в двух конструктивных вариантах — корпусном и бескопусном. Бескорпуснаямикросхема — этополупроводниковыйкристалл,предназначенныйдлямонтажав гибридную микросхемуилимикросборку. Корпус — эточастьконструкциимикросхемы,предназначеннаядлязащитыотвнешнихвоздействийи для соединенияс внешнимиэлектрическимицепямипосредствомвыводов.Корпусастандартизованыдля упрощениятехнологическогопроцессаизготовленияизделийизразныхмикросхем.

Вроссийскихкорпусахрасстояниемеждувыводамиизмеряетсяв миллиметрахи наиболеечастоэто2,5мм или1,25мм.У импортныхмикросхемрасстояниеизмеряютв дюймах,используявеличину1/10или1/20 дюйма,чтосоответствует2,54и1,28мм.В корпусахдо16выводовэтаразницанезначительна,а при большихразмерахидентичныекорпусауженесовместимы.В современныхимпортныхкорпусахдляповерхностногомонтажаприменяюти метрическиеразмеры:0,8мм;0,65мми другие [4].

Технология сверхбольших интегральных схем определяет прогресс в передовых областях науки и техники и является основой для развития высокотехнологичных отраслей отечественной промышленности. Она имеет широкий спектр применений: от бытовой аппаратуры до специализированных устройств оборонной техники. Мировой рынок интегральных схем практически неисчерпаем, что позволит создавать высокорентабельные ориентированные на экспорт производства

В настоящее время основная часть производимых интегральных схем в мире соответствует минимальным рабочим размерам элементов 0,8–1,0 мкм. Ведущие зарубежные фирмы США, Японии и Южной Кореи имеют заводы, выпускающие высокопроизводительные микропроцессоры и ультра большие схемы памяти с минимальными размерами 0,5 мкм.

В Казахстане имеются пилотные линии для производства кремниевых интегральных схем с минимальными размерами рабочих элементов 0,8–1 мкм. В ближайшее время будет завершено создание производства схем с размерами элементов на уровне 0,5 мкм. Освоение этих линий позволит Казахстану полностью обеспечить внутреннюю потребность кремниевыми схемами отечественного производства сложностью до сотен тысяч транзисторов на кристалле и выйти на мировой рынок [3].

Создание научно-технического задела в области перспективных технологий и устройств микро и наноэлектроника дает возможность модернизировать производство и расширить объем экспорта отечественных электронных компонентов.

Что такое интегральная микросхема

Интегральная схема – это изделие из микроэлементов с высокой миниатюризацией. Эти элементы преобразуют и обрабатывают сигналы. Сама схема имеет высокую плотность самих элементов. Такие элементы называются компонентами и выполняют ту или иную задачу. Эти схемы могут быть разной сложности и типов – от самых простых до сложнейших.

Используются ИС в создании компьютеров, различной вычислительной техники и другом оборудовании, в том числе промышленном и бытовом. Более подробно о строении, использовании, а также развитии интегральных схем будет рассказано в данной статье. В качестве информационного дополнения, в материале содержатся два подробных видеоролика и один скачиваемые файл о строении ИС.

Интегральные микросхемы

По научному определению, интегральные микросхемы – это отдельные высокотехнологичные устройства (с огромным количеством электронных компонентов, заключенных в маленьком корпусе), которые выполняют какую-то функцию или действие. Этих функций может быть или одна или несколько. Вот список некоторых основных функций, которые выполняют интегральные микросхемы:

Интегральные микросхемы представляют собой изделие, выполненное в герметизированном (металлическом, пластмассовом, керамическом, металлокерамическом и так лале) корпусе. Микросхемы бывают различного исполнения (прямоугольные, треугольные, круглые) с разным количеством выводов: от трех (например, на стабилизаторе LM7805, до нескольких сотен на процессорах).

Интегральные микросхемы (и аппаратура на них) обладают неоспоримыми преимуществами:

Микросхемы разделяют на два вида: 1 – полупроводниковые интегральные схемы; 2 – гибридные интегральные схемы.

Полупроводниковые интегральные элементы представляют собой кристалл, в глубине которого выполняют все элементы схемы. Изоляция различных элементов осуществляют с помощью (так называемых) «p-n» переходов.

Гибридные интегральные схемы выполняются по «пленочной» технологии и представляют пластину (подложку) из диэлектрического материала. На нее нанесены (в виде пленок) плоские компоненты (резисторы, дроссели, конденсаторы и т. д.) и соединения. Причем сопротивление резисторов может быть 105 Ом, емкость конденсаторов 103 пФ, а дроссели иметь индуктивность около 10 мкГн – не более.

Транзисторы, диоды, магнитные элементы, конденсаторы более 103 пФ и электролитические выполняют с помощью навесного монтажа. Гибридные интегральные схемы имеют более высокую точность параметров (на один или два порядка выше), чем полупроводниковые аналоги. Количество элементов внутри каждого класса микросхем может достигать несколько тысяч.

Степень интеграции

Ранее использовались также теперь устаревшие названия: ультрабольшая интегральная схема (УБИС) — до 1 миллиарда элементов в кристалле и гигабольшая интегральная схема (ГБИС) — более 1 миллиарда элементов в кристалле, но в настоящее время название УБИС и ГБИС практически не используется (например, последние версии процессоров Itanium, 9300 Tukwila, содержат два миллиарда транзисторов), и все схемы с числом элементов, превышающим 10 000, относят к классу СБИС.

Элемент интегральной схемы

Часть интегральной схемы, реализующая функцию какого-либо электрорадиоэлемента (резистора, диода, транзистора и т. д.), причем эта часть выполнена нераздельно от других частей и не может быть выделена как самостоятельное изделие с точки зрения требований к испытаниям, приемке, поставке и эксплуатации. Компонент интегральной схемы в отличие от элемента может быть выделен как самостоятельное изделие с указанной выше точки зрения.

По конструктивно-технологическим признакам интегральные схемы обычно разделяют на:

В полупроводниковой схеме все элементы и межэлементные соединения выполнены в объеме или на поверхности полупроводника. В таких схемах нет компонентов. Это наиболее распространенная разновидность интегральных схем.

Интегральную схему называют гибридной, если она содержит компоненты и (или) отдельные кристаллы полупроводника. В пленочных интегральных схемах отдельные элементы и межэлементные соединения выполняются на поверхности диэлектрика (обычно используется керамика). При этом применяются различные технологии нанесения пленок из соответствующих материалов. По функциональным признакам интегральные схемы подразделяют на аналоговые (операционные усилители, источники вторичного электропитания и др.) и цифровые (логические элементы, триггеры и т. п.).

Краткая историческая справка

Первые опыты по созданию полупроводниковых интегральных схем были осуществлены в 1953 г., а промышленное производство интегральных схем началось в 1959 г. В 1966 г. был начат выпуск интегральных схем средней степени интеграции (число элементов в одном кристалле до 1000). В 1969 г. были созданы интегральные схемы большей степени интеграции (большие интегральные схемы, БИС), содержащие до 10000 элементов в одном кристалле.

К 2000 г. ожидается появление интегральных схем, содержащих до 100 млн МОП транзисторов в одном кристалле (речь идет о цифровых схемах). Система обозначений. Условное обозначение интегральных микросхем включает в себя основные классификационные признаки.

К этим основным элементам обозначений микросхем могут добавляться и другие классификационные признаки.

Дополнительная буква в начале четырехэлементного обозначения указывает на особенность конструктивного исполнения:

В начале обозначения для микросхем, используемых в условиях широкого применения, приводится буква К.

Серии бескорпусных полупроводниковых микросхем начинаются с цифры 7, а бескорпусные аналоги корпусных микросхем обозначаются буквой Б перед указанием серии.

Через дефис после обозначения указывается цифра, характеризующая модификацию конструктивного исполнения:

Как создаются интегральные схемы?

Как изготовить чип памяти или процессор компьютера? Процесс производства начинается с химического элемента — кремния, который химически обрабатывается (легируется) для придания различных электрических свойств.

Современное исполнение интегральной схемы (одна из многочисленных форм), установленной на электронной плате устройства. Это далеко не самый продвинутый вариант, а лишь один из многих

Традиционно для нужд электроники используются материалы двух категорий:

Принцип легирования химических элементов

Если добавить некоторое количество сурьмы кремнию, структура этого химического элемента насыщается большей массой электронов, чем обычно. Обеспечивается проводимость электричества. Кремний, «легированный» подобным образом, приобретает характеристику N-типа. В другом случае, когда вместо сурьмы добавляется бор, масса электронов кремния уменьшается, оставляя своеобразные «дыры», которые функционируют подобно «отрицательно заряженным электронам».

Благодаря «дырам» положительный электрический ток пропускается в противоположном направлении. Такая разновидность кремния характеризуется P-типом. Расположение областей кремния N-типа и P-типа рядом одна с другой, способствует созданию соединения, где отмечается поведение электронов, характерное для электронных компонентов на основе полупроводников:

Структурная интегральная схема внутри чипа

Итак, процесс создания интегральной схемы начинается от монокристалла кремния, напоминающего по форме длинную сплошную трубу, «нарезанную» тонкими дисками — пластинами. Такие пластины размечаются на множество одинаковых квадратных или прямоугольных областей, каждая из которых представляет один кремниевый чип (микрочип). Пример внутренней структуры интегральной схемы, демонстрирующий возможности такой уникальной технологии интеграции полноценных электронных схемотехнических решений.

Затем на каждом таком чипе создаются тысячи, миллионы или даже миллиарды компонентов путём легирования различных участков поверхности — превращения в кремний N-типа или P-типа. Легирование осуществляется различными способами. Один из вариантов — распыление, когда ионами легирующего материала «бомбардируют» кремниевую пластину.

Другой вариант — осаждение из паровой фазы, включающий введение легирующего материала газовой фазой с последующей конденсацией. В результате такого ввода примесные атомы образуют тонкую пленку на поверхности кремниевой пластины. Самым точным вариантом осаждения считается молекулярно-лучевая эпитаксия.

Конечно, создание интегральных микросхем, когда упаковываются сотни, миллионы или миллиарды компонентов в кремниевый чип размером с ноготь, видится сложнейшим процессом. Можно представить, какой хаос принесёт даже небольшая крупинка в условиях работы в микроскопическом (наноскопическом) масштабе. Вот почему полупроводники производятся в лабораторных условиях безупречно чистых. Воздух лабораторных помещений тщательно фильтруется, а рабочие обязательно проходят защитные шлюзы и облачаются в защитную одежду.

Кто создал интегральную схему?

Разработка интегральной схемы приписывается двум физикам — Джеку Килби и Роберту Нойсу, как совместное изобретение. Однако фактически Килби и Нойс вынашивали идею интегральной схемы независимо друг от друга. Между учёными даже существовала своего рода конкуренция за права на изобретение.

Джек Килби трудился в «Texas Instruments», когда учёному удалось реализовать идею монолитного принципа размещения различных частей электронной схемы на кремниевом чипе. Учёный вручную создал первую в мире интегральную микросхему (1958 год), использовав чип на основе германия. Компания «Texas Instruments» спустя год подала заявку на патент.

Тем временем представитель другой компании «Fairchild Semiconductor» — Роберт Нойс, проводил эксперименты с миниатюрными цепями своего устройства. Благодаря серии фотографических и химических методов (планарный процесс), учёный всего лишь на год позже Килби создал практичную интегральную схему. Методика получения также была оформлена заявкой на патент.

Критерий взаимодействия ИМС в устройствах (электрический аспект). Практические вопросы электрического сопряжения (стр. 2 )

| Из за большого объема этот материал размещен на нескольких страницах: 1 2 3 |

Счетчики строятся из разрядных схем, имеющих межразрядные связи. Соответственно организации этих связей различают счетчики с последовательным, параллельным и комбинированными переносами.

Возможные режимы работы счетчика:

— регистрация числа поступивших на счетчик сигналов;

В первом режиме результат — содержимое счетчика, во втором режиме выходными сигналами являются импульсы переполнения счетчика.

Быстродействие счетчика характеризуется временем установления в нем нового состояния (первый режим), а также максимальной частотой входных сигналов fmax.

Как и любой автомат, счетчик можно строить на триггерах любого типа, однако удобнее всего использовать для этого триггеры типа Т (счетные) и JK, имеющие при J = К = 1 счетный режим.

Состояние счетчика читается по выходам разрядных схем как слово Qn-1Qn-2—Q0, входные сигналы поступают на младший разряд счетчика.

Двоичным счетчиком называется счетчик, имеющий модуль М = 2n, где n — целое число, и естественную последовательность кодов состояний (его со стояния отображаются последовательностью двоичных чисел, десятичными эквивалентами которых будут числа 0, 1, 2, 3. M-l).

16. БИС, СБИС, запоминающие устройства – классификация, основные характеристики, современное состояние

Элементную базу цифровых устройств (ЦУ) составляют интегральные схемы (ИС). Характеристикой сложности ИС является уровень интеграции, оцениваемый либо числом базовых логических элементов, либо числом транзисторов, которые могут быть реализованы на кристалле. Различия в уровне интеграции делят ИС на несколько категорий: МИС, СИС, БИС, СБИС (соответственно малые, средние, большие и сверхбольшие ИС).

Микропроцессор способен выполнять команды, входящие в его систему команд. Меняя последовательность команд (программу), можно решать различные задачи на одном и том же микропроцессоре. Иначе говоря, в этом случае структура аппаратных средств не связана с характером решаемой задачи.

В виде БИС/СБИС с программируемой структурой потребителю предлагается кристалл, содержащий множество логических блоков, межсоединения для которых назначает сам системотехник. Промышленность получает возможность производить кристаллы массовым тиражом, не адресуясь к отдельным потребителям. Системотехник сам программирует структуру ИС соответственно своему проекту.

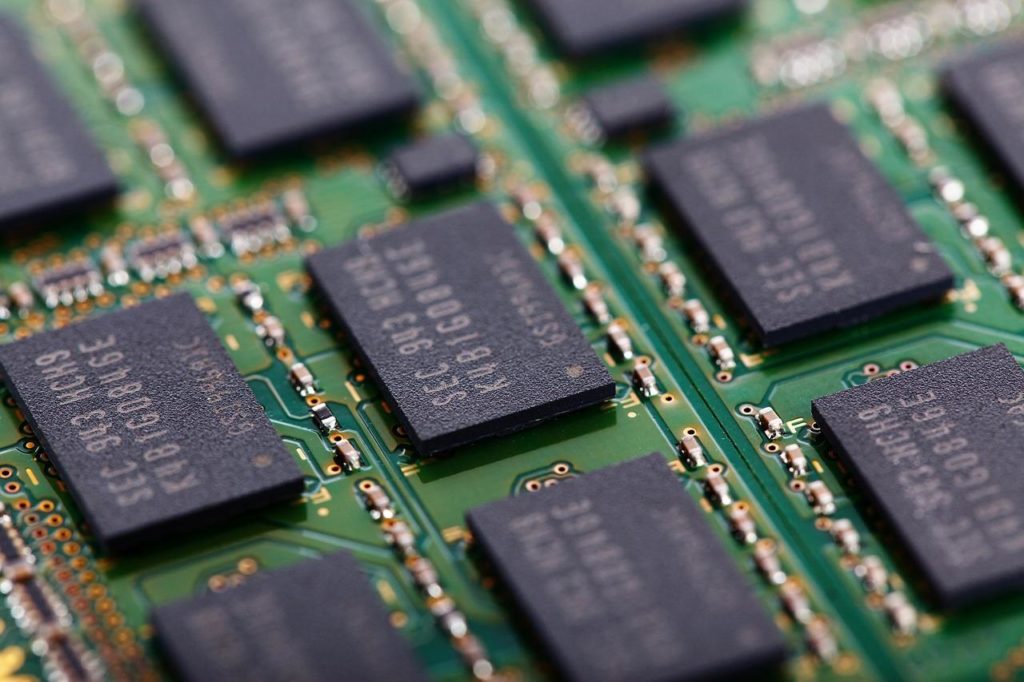

Запоминающие устройства (ЗУ) служат для хранения информации и обмена ею с другими ЦУ. Микросхемы памяти в общем объеме выпуска ИС занимают около 40% и играют важнейшую роль во многих системах различного назначения. В настоящее время созданы и используются десятки различных типов ЗУ.

Основные характеристики ЗУ:

Информационная емкость — максимально возможный объем хранимой информации. Выражается в битах или словах (в частности, в байтах). Бит хранится запоминающим элементом (ЗЭ), а слово — запоминающей ячейкой (ЗЯ), т. е. группой ЗЭ, к которым возможно лишь одновременное обращение.

Организация ЗУ— произведение числа хранимых слов на их разрядность. Видно, что это дает информационную емкость ЗУ, однако при одной и той же информационной емкости организация ЗУ может быть различной, так что организация является самостоятельным важным параметром.

Быстродействие (производительность) ЗУ оценивают временами считывания, записи и длительностями циклов чтения/записи. Время считывания — интервал между моментами появления сигнала чтения и слова на выходе ЗУ. Время записи — интервал после появления сигнала записи, достаточный для установления ЗЯ в состояние, задаваемое входным словом. Минимально допустимый интервал между последовательными чтениями или записями образует соответствующий цикл. Длительности циклов могут превышать времена чтения или записи, т. к. после этих операций может потребоваться время для восстановления необходимого начального состояния ЗУ.

Для классификации ЗУ важнейшим признаком является способ доступа к данным.

При адресном доступе код на адресном входе указывает ячейку, с которой ведется обмен. Все ячейки адресной памяти в момент обращения равнодоступны. Эти ЗУ наиболее разработаны, и другие виды памяти часто строят на основе адресной с соответствующими модификациями.

Адресные ЗУ делятся на RAM (Random Access Memory) u ROM (Read-Only Memory). Оперативные ЗУ хранят данные, участвующие в обмене при исполнении текущей программы, которые могут быть изменены в произвольный момент времени. Запоминающие элементы ОЗУ, как, правило, не обладают энергонезависимостью. В ROM содержимое либо вообще не изменяется, либо изменяется, но редко и в специальном режиме.

RAM делятся на статические и динамические. В первом варианте запоминающими элементами являются триггеры, сохраняющие свое состояние, пока схема находится под питанием и нет новой записи данных. Во втором варианте данные хранятся в виде зарядов конденсаторов, образуемых элементами МОП-структур. Саморазряд конденсаторов ведет к разрушению данных, поэтому они должны периодически (каждые несколько миллисекунд) регенерироваться. Статические ЗУ называются SRAM (Static RAM), а динамические — DRAM (Dynamic RAM). Динамические ЗУ характеризуются наибольшей информационной емкостью и невысокой стоимостью, поэтому именно они используются как основная память ЭВМ

Статические ОЗУ можно разделить на асинхронные, тактируемые и синхронные (конвейерные). В асинхронных сигналы управления могут задаваться как импульсами, так и уровнями. В тактируемых ЗУ некоторые сигналы обязательно должны быть импульсными. Этот тип ЗУ называют часто синхронным.

В ЗУ с последовательным доступом записываемые данные образуют некоторую очередь. Считывание происходит из очереди слово за словом либо в порядке записи, либо в обратном порядке. Ассоциативный доступ реализует поиск информации по некоторому признаку, а не по ее расположению в памяти (адресу или месту в очереди).

17. Особенности стандартных микросхем счетчиков, способы наращивания.

К счетчикам относят, автоматы, которые под действием входных импульсов переходят из одного состояния в другое, фиксируя тем самым число поступивших на их вход импульсов в том или ином коде.

Часто используются следующие типономиналы: ИЕ10 – асинхронный RESET, синхронная предустановка PE и ИЕ18 – синхронный RESET, синхронная предустановка PE

R – сброс – т. е. очистка всех разрядов счетчика, Din – используется для предустановки счетчика – при подаче «0» на PE# счетчик захватывает с нее данные. Q – выходная шина.

С – вход синхолнизауии, CR – выход группового переноса для наращивания размерности счетчика ( «1» появляется при переполнении счетчика)

Также могут быть два дополнительных входа – CET – разрешение счета (также называемый трюковым) и CEP – разрешение переноса. Эти входы также используются для наращивания размерности счетчика.

Схема наращ-я размер-ти с исп-м послед-го межсекционного переноса:

Схема наращ-я размер-ти с исп-м параллельного межсекционного переноса:

Структура умножителей тесно связана со структурой математических выражений, описывающих операцию умножения.

Пусть имеются два целых двоичных числа без знаков Аm= аm-1. a0 и Вn = bn-1. b0. Их перемножение выполняется по известной схеме «умножения столбиком». Если числа четырехразрядные, т. е. m = n = 4, то

Перемножители могут быть просто множительными блоками (МБ) или множительно-суммирующими (МСБ), последние обеспечивают удобство наращивания размерности умножителя.

МСБ реализует операцию Р = Аm х Вn + Сm + Dn, т. е. добавляет к произведению два слагаемых: одно разрядности m, совпадающей с разрядностью множимого, другое разрядности n, совпадающей с разрядностью множителя.

Схема множительного блока отличается от схемы МСБ тем, что в ней отсутствуют сумматоры правой диагонали, т. к. при Сm = 0 и Dn = 0 они не требуются.

Построение умножителей большей размерности из умножителей меньшей размерности на основе МБ требует введения дополнительных схем, называемых «деревьями Уоллеса», которые имеются в некоторых зарубежных сериях. При использовании МСБ дополнительные схемы не требуются.

Типовая структура параллельного умножителя может быть представлена в следующем виде:

Цифровые элементы (логические, запоминающие, буферные) могут иметь выходы следующих типов: логические, с открытым коллектором (стоком), с третьим состоянием, с открытым эмиттером (истоком).

Логический выход формирует два уровня выходного напряжения (U0 и U1). Выходное сопротивление логического выхода стремятся сделать малым, способным развивать большие токи для перезаряда емкостных нагрузок и, следовательно, получения высокого быстродействия элемента.

Особенность таких выходов состоит в том, что их нельзя соединять параллельно. Во-первых, это создает логическую неопределенность, т. к. в точке соединения выхода, формирующего логическую единицу, и выхода, формирующего логический нуль, не будет нормального результата. Во-вторых, при соединении выходов, находящихся в различных логических состояниях, возникло бы их «противоборство». Вторая особенность логического выхода двухтактного типа связана с протеканием через оба транзистора коротких импульсов тока при переключениях из одного логического состояния в другое (появление помех)

Элементы с тремя состояниями выхода (типа ТС) кроме логических состояний 0 и 1 имеют состояние «отключено», в котором ток выходной цепи пренебрежимо мал. В это состояние (третье) элемент переводится специальным управляющим сигналом, обеспечивающим запертое состояние обоих транзисторов выходного каскада (Т1 и Т2 на рис. 1.3, а). Сигнал управления элементом типа ТС обычно обозначается как ОЕ (Output Enable). При наличии разрешения (ОБ = 1) элемент работает как обычно, выполняя свою логическую операцию, а при его отсутствии (ОЕ = 0) переходит в состояние «отключено».

Выходы типа ТС отмечаются в обозначениях элементов значком треугольника или буквой Z. Выходы типа ТС можно соединять параллельно при условии, что в любой момент времени активным может быть только один из них. В этом случае отключенные выходы не мешают активному формировать сигналы в точке соединения выходов. Элементы типа ТС сохраняют такие достоинства элементов с логическим выходом как быстродействие и высокая нагрузочная способность.

Элементы с открытым коллектором имеют выходную цепь, заканчивающуюся одиночным транзистором, коллектор которого не соединен с какими-либо цепями внутри микросхемы (рис. 1.5, a). Транзистор управляется от предыдущей части схемы элемента так, что может находиться в насыщенном или запертом состоянии. Насыщенное состояние трактуется как отображение логического нуля, запертое — единицы.

Для формирования высокого уровня напряжения при запирании транзистора на выходе элементов с открытым коллектором (типа ОК) требуется подключать внешние резисторы (или другие нагрузки), соединенные с источником питания.

(При реализации монтажной логики высокое напряжение на общем выходе возникает только при запирании всех транзисторов, т. к. насыщение хотя бы одного из них снижает выходное напряжение до уровня

Выход с открытым эмиттером характерен для элементов типа ЭСЛ. Для работы на магистраль такие элементы не используются. Возможность соединять друг с другом выходы с открытым эмиттером при объединении эмиттерных резисторов в один общий резистор приводит к схеме, иногда называемой «эмиттерный дот» и используемой при построении логических схем для получения дополнительной операции монтажной логики. Элементы ЭСЛ имеют противофазные выходы, на одном из которых реализуется функция ИЛИ, на другом — ИЛИ-НЕ. Соединяя прямые выходы нескольких элементов, получают расширение по ИЛИ (входные переменные соединяемых элементов образуют единую дизъюнкцию). Соединяя инверсные выходы, получают операцию И-ИЛИ относительно инверсий входных переменных

20. SRAM – способы, режимы записи/чтения

· Синхронное (конвейерное) – для облегчения чтения, в тракт ввода данных перед выходным буфером включают синхронный конвейерный регистр.

· Пакетное (Burst) – при пакетном доступе адрес первого элемента – внешний (от процессора или контроллера). Последующие адрес формируются самой схемой (внутренней пакетной логикой). Обычно размер пакета – 4 элемента. Ориентируясь на различные процессоры пользователь может выбрать 1 из 2-х режимов формирования адресов элемента пакета (кроме первого): последовательный по содержимому внутреннего 2-х разрядного счетчика, либо с чередованием четных\нечетных адресов.

· Асинхронная, стандартная – данные для записи подаются в том же цикле, что и адрес.

· Запаздывающая запись (поздняя запись) в приборах синхронного типа – данные для записи подаются не в цикле ввода адресов, а в следующем.

· ZeroBus TurnAround (ZBT) – нет мертвых циклов

При проектировании SRAM асинхронного типа особое внимание следует уделять режимным параметрам для операции записи – время предустановки адреса относительно момента окончания сигнала разрешения записи, длительность сигнала записи, время сохранения адреса относительно окончания сигнал записи, время предустановки и сохранения записанных данных относительно окончания сигнала записи.

21. Приемы построения двоично-кодированных счетчиков с произвольным модулем счета

Счетчики с модулем, не равным целой степени числа 2, т. е. с произвольным модулем, реализуются на основе нескольких методов. Для построения счетчика с произвольным модулем М берется разрядность

Способы исключения лишних состояний многочисленны, и для любого М можно предложить множество реализации счетчика. Исключая некоторое число первых состояний, получим ненулевое начальное состояние счетчика, что приводит к отсутствию естественного порядка счета и регистрации в счетчике кода с избытком. Исключение последних состояний позволяет сохранить естественный порядок счета.

В счетчиках с исключением последних состояний счет ведется обычным способом, вплоть до достижения числа М—1. Далее последовательность переходов счетчика в направлении роста регистрируемого числа должна быть прервана, и следующее состояние должно быть нулевым. При этом счетчик будет иметь М внутренних состояний (от 0 до М—1), т. е. его модуль равен М. Если предполагается использовать асинхронный сброс, то он осуществляется по достижении состояния M, а при синхронном сбросе – (M-1).

Рассмотрим два способа построения счетчиков с произвольным модулем: модификации межразрядных связей и управлении сбросом. При построении счетчика с модифицированными межразрядными связями последние, лишние, состояния исключаются непосредственно из таблицы функционирования счетчика. При этом после построения схемы обычным для синтеза автоматов способом получается счетчик, специфика которого состоит в нестандартных функциях возбуждения триггеров, и, следовательно, в нестандартных связях между триггерами, что и объясняет название способа. Схема получается как специализированная, изменение модуля счета требует изменения самой схемы, т. е. легкость перестройки с одного модуля на другой отсутствует. В то же время реализация схемы счетчика может оказаться простой.

При управлении сбросом выявляется момент достижения содержимым счетчика значения М—1 (или M при использовании асинхронного сброса, но это чревато установлением гонок сигналов и в ряде случаев делает невозможным выполнение требований изготовителем микросхем к режимным параметрам). Это является сигналом сброса счетчика в следующем такте, после чего начинается новый цикл. Этот вариант обеспечивает легкость перестройки счетчика на другие значения модуля, т. к. требуется изменять лишь код, с которым сравнивается содержимое счетчика для выявления момента сброса.

22. PROM – типовая структура на кристалле, УГО, основные параметры, характеристика развития.

В ЗУ типа PROM микросхемы программируются устранением или созданием специальных перемычек (в настоящее время используется также программирование электронным способом – память EPROM, но без кварцевого окна). В исходной заготовке имеются (или отсутствуют) все перемычки. После программирования остаются или возникают только необходимые.

Среди отечественных PROM ведущее место занимают микросхемы серии К556, имеющие информационную емкость 1. 64 Кбит и время доступа по адресу 70. 90 нc., также используется серия К1556

Внешняя организация памяти типа PROM проста: входными сигналами служат адресный код и сигнал выбора микросхемы CS. Во времени последовательность сигналов следующая: вначале подается адресный код (чтобы произошла дешифрация адреса и было исключено обращение к непредусмотренной ячейке), затем поступает сигнал выбора микросхемы CS и после задержки, определяемой быстродействием схемы, на выходах данных устанавливаются правильные значения считываемых сигналов.

Микросхемы памяти PROM построены по структуре 2DM. Это значит, что адрес разветвляется внутри на 2 компоненты, каждая декодируется своим дешифратором. Дешифратор строк активирует 1 единственную строку в матрице запоминающих ячеек. С этой считывается n m-разрядных слов. А дешифратор колонки обеспечивает выбор адресного слова из этого множества слов для вывода его через выходные буферы.

Tba – время выборки адреса.

23. Структура устройства синхронизации, требования к частоте задающего генератора. Пример схемы генератора с кварцевой стабилизацией частоты.

Обобщенная схема устройства синхронизации (задающий генератор, схема формирования синхропоследовательности, размножитель):

От задающего генератора требуется выдача стабильной частоты для предотвращения общего снижения тактовой частоты (а значит и производительности) ф-х узлов. Требуемая стабильность частоты – не менее 10-4 – 10-5 (предпочтительно использование кварцевого генератора).

Пример схемы кварцевого генератора:

24. Структура операционного блока с разрядно-модульной организацией. Подход к расчету времени цикла.

Типовой операционный блок содержит: микропроцессорную секцию (МПС), обрамленную внешней логикой сдвигов, регистр состояния, мультиплексор кода условия и регистр выходных данных. Управление МПС осуществляется операционным полем МК в соответствии с системой микрокоманд и форматом микроинструкций.

Внешняя для МПС логика сдвигов участвует в выполнении логич-х, арифметических и циклических сдвигов. Управление логикой сдвигов осуществляется разрядами МК, которые задают тип сдвига.

Регистр состояния и мультиплексор кода условия предназначены для хранения слова состояния процессорной секции и передачи требуемого признака в МУУ. Выбор в качестве признака ветвления одного из битов регистра для текущей МК выполняется мультиплексором под управлением разрядов МК, кодирующих условие перехода.

25. Причины и следствие расфазировки синхросигналов. Способы устранения. Умножение частоты синхросигналов (PLL)

Под расфазировкой синхросигналов понимают изменение временного положения используемого синхросигнала относительно опорного. Причины расфазировки:

Обычно тактовые импульсы задаются одним генератором, а используются иногда тысячами и более элементов памяти. Попытка применить мощный генератор с разводкой от него синхросигналов по всем элементам памяти для сложных устройств оказывается, как правило, неудачной, в первую очередь из-за помех, вызываемых сильноточными цепями синхронизации. Типовое решение – размножение синхросигнала с помощью пирамидальной структуры, однако из-за неодинаковости задержек на разных блоках размножителя, выходные синхропоследовательности могут быть сдвинуты по фазе.

В высокоскоростных конвейерах расфазировка синхросигналов, полученных конвейерными регистрами, может привести к «проскоку» новой информации через ступень конвейера и сбою в его работе. Расфазировка усугубляется разбросом пороговых уровней КМОП входных каскадов.

Для устранения расфазировки применяют средства фазовой автоматической подстройки частоты (ФАПЧ)(PLL)

PLL содержат фазовый компаратор ФК, генератор, управляемый напряжением ГУН (VCO, Volt-Controlled Oscillator), с выхода которого берутся скорректированные синхроимпульсы, и цепь обратной связи, в которую могут быть включены не только элементы задержки, но и делители частоты ДЧ. При этом на PLL могут возлагаться две функции — коррекция фазовых сдвигов синхросигналов (Clock Skew), осуществляемая замкнутым контуром с элементом задержки в обратной связи (функция Clock Lock), и получение удвоенной частоты синхросигналов при введении в цепь обратной связи делителя частоты ДЧ (функция Clock Boost). Удвоение внутренней частоты работы устройств относительно внешней частоты передачи данных часто используется в микропроцессорах и СБИС программируемой логики высокой сложности.

Благодаря введению схем PLL, удается снижать расфазирование тактовых сигналов системы до очень малых значений.

26. Пример архитектуры CPLD

Сложные программируемые логические устройства архитектурно произошли от РLD типа РАL (ПМЛ) и в английской терминологии называются СРLD.

CPLD состоят из программируемой матрицы соединений ПМС, множества функциональных блоков ФБ, подобных ПМЛ, и блоков ввода/вывода (БВВ)

В целом CPLD представляет собой объединение нескольких РАL (ПМЛ) в единое устройство средствами программируемой коммутационной матрицы. Кроме ОСНОВНЫХ блоков СРLD на схеме показаны контроллеры интерфейса JTAG и ISP. используемые для конфигурирования и тестирования создаваемых структур.

Число ФБ, входящих в состав СРLD, изменяется в широких пределах в зависимости от СЛОЖНОСТН данной микросхемы. Выходы ФБ, число которых n, подключены как к программируемой матрице соединений ПМС, так и к блокам ввода/вывода БВВ. Блоки ввода/вывода связаны с внешними двунаправленными выводами. Три вывода (на схеме слева внизу) специализированы и предназначены для глобальных, т. е. общих для всей схемы, сигналов тактирования GСК, управления сбросом/установкой GSR, управления третьим состоянием GTS. Возможно и иное использование специализированных выводов, если они не применяются по назначению. Число контактов ввода/вывода может быть меньше числа выводов всех ФБ. В этом случае часть макроячеек может быть использована только для выработки внутренних сигналов устройства (сигналов обратных связей), потребность в которых типична для многих видов устройств.

27. EPROM – принцип работы запоминающего элемента, временная диаграмма чтения, характеристика современных устр-в.

В репрограммируемых ЗУ типа EPROM возможно стирание старой информации и замена ее новой в результате специального процесса, для проведения которого ЗУ выводится из рабочего режима. Рабочий режим (чтение данных) — процесс, выполняемый с относительно высокой скоростью. Замена же содержимого памяти требует выполнения гораздо более длительных операций.

Запоминающими элементами современных РПЗУ являются транзисторы типов МНОП и ЛИЗМОП (добавление ЛИЗ к обозначению МОП происходит от слов Лавинная Инжекция Заряда). МНОП-транзистор отличается от обычного МОП-транзистора двухслойным подзатворным диэлектриком.

Рис. Структуры транзисторов типов МНОП (а) и ЛИЗМОП с двойным затвором (б)

На поверхности кристалла расположен тонкий слой двуокиси кремния SiO2, далее более толстый слой нитрида кремния Si3N4 и затем уже затвор. На границе диэлектрических слоев возникают центры захвата заряда. Благодаря туннельному эффекту, носители заряда могут проходить через тонкую пленку окисла толщиной не более 5 нм и скапливаться на границе раздели слоев. Этот заряд и является носителем информации, хранимой МНОП-транзистором. Заряд записывают созданием под затвором напряженности электрического поля, достаточной для возникновения туннельного перехода носителей заряда через тонкий слой SiO2. На границе раздела диэлектрических слоев можно создавать заряд любого знака в зависимости от направленности электрического поля в подзатворной области. Наличие заряда влияет на пороговое напряжение транзистора. Для МНОП-транзистора с n-каналом отрицательный заряд на границе раздела слоев повышает пороговое напряжение (экранирует воздействие положительного напряжения на затворе, отпирающего транзистор). При этом пороговое напряжение возрастает настолько, что рабочие напряжения на затворе транзистора не в состоянии его открыть (создать в нем проводящий канал). Транзистор, в котором заряд отсутствует или имеет другой знак, легко открывается рабочим значением напряжения. Так осуществляется хранение бита в МНОП: одно из состояний трактуется как отображение логической единицы, другое — нуля.

Транзисторы типа ЛИЗМОП всегда имеют так называемый плавающий затвор, который может быть единственным или вторым, дополнительным к обычному (управляющему) затвору. Транзисторы с одним плавающим затвором используются в ЗУ типа РПЗУ-УФ, а с двойным затвором пригодны как в РПЗУ-УФ, так и в РПЗУ-ЭС. Принцип работы ЛИЗМОП близок к МНОП-транзистору — здесь также между управляющим затвором и областью канала помещается область, в которую при программировании можно вводить заряд, влияющий на величину порогового напряжения транзистора. Только область введения заряда представляет собою не границу раздела слоев диэлектрика, а окруженную со всех сторон диэлектриком проводящую область (обычно из поликристаллического кремния), в которую, как в ловушку, можно ввести заряд, способный сохраняться в ней в течение очень длительного времени. Эта область и называется плавающим затвором.

Микросхемы памяти EPROM построены по структуре 2DM. Это значит, что адрес разветвляется внутри на 2 компоненты, каждая декодируется своим дешифратором. Дешифратор строк активирует 1 единственную строку в матрице запоминающих ячеек. С этой считывается n m-разрядных слов. А дешифратор колонки обеспечивает выбор адресного слова из этого множества слов для вывода его через выходные буферы.

Tba – время выборки адреса.

28. Функции секвенсора микрокоманд (внутри счетчик циклов), их реализация в иллюстративной структуре

Ядром MT1804 является микропрограммное устройство управления, которое в свою очередь состоит из секвенсора микрокоманд, МПП и регистра микрокоманд. Секвенсор микрокоманд определяет последовательность выполнения МК и состоит из БМУ (блок микрокомандного управления), мультиплексора(вот это можно и пропустить) и контроллера БМУ (контроллер осуществляет тестирование признака ветвления, поступающего на операционного блока на вход TST и преобразует код P3…P0 управления следующим адресом, задаваемым разрядами МК (27…24), в сигналы, управляющие выбором следующего адреса в БМУ).

29. SRAM асинхронного типа – структура на кристалле, наращивание информационной емкости, временные диаграммы, режимные параметры

Статические ОЗУ (SRAM), как правило, имеют структуру 2DM, часть их при небольшой информационной емкости строится по структуре 2D.

Запоминающими элементами статических ОЗУ служат триггеры с цепями установки и сброса. В связи с этим статические ОЗУ называют также триггерными.

Внешняя организация статического ЗУ емкостью 64 Кбита (8Кх8) показана на рисунке. Состав и функциональное назначение сигналов адреса А12-0, выборки кристалла

Имеется также вход

Функционирование ЗУ во времени регламентируется временными диаграммами, устанавливаемыми изготовителем. В основу кладутся определенные требования. Например, чтобы исключить возможность обращения к другой ячейке, рекомендуется подавать адрес раньше, чем другие сигналы, с опережением на время его декодирования. Адрес должен держаться в течение всего цикла обращения к памяти.

Рис. Временные диаграммы процессов чтения (а) и записи (б) в статическом ЗУ

На диаграммах показаны времена выборки относительно адреса tA и выбора tcs длительности импульсов tw различных сигналов и цикла адреса tSY(A), задержка tSU перехода выхода из активного состояния в состояние отключено, времена предустановки tSU и удержания tH с указанием сигналов, для которых они отсчитываются. Приведено время восстановления trec(WR) отсчитываемое как необходимая пауза между повторениями активных интервалов сигнала WR.

Для правильного проектирования модулей памяти и использования в них конкретных микросхем необходимо также знать емкости их входов С1, выходов С0, и предельно допустимую емкость нагрузки CLmax.