Большая Энциклопедия Нефти и Газа

Потенциальный способ

В устройствах типа 3420 для записи с плотностью до 32 импульсов на 1 мм используется способ записи без возврата к нулю, а фазовый потенциальный способ применяется для записи с плотностью 64 импульса на 1 мм. Запись новой информации на ленту осуществляется записывающей головкой, считывающая же головка читает только что записанную информацию. Если прочитанное не совпадает с тем, что должно быть записано, выдается сигнал об ошибке. При чтении информации, записанной ранее, лента проходит под теми же головками и читается ими обеими. [19]

Основные способы физического представления информации в схемах с логическими элементами: потенциальный, импульсный и динамический. При потенциальном способе двум значениям переменной 0 и 1 соответствуют высокий и низкий уровень напряжения. [22]

В качестве элементно-технологической базы современных автоматов используют интегральные схемы, в которых применяют потенциальный способ представления и переработки информации. [25]

Среди дисперсных пород и их моделей следует различать матричные и статистические, которые могут быть рассчитаны путем решения дифференциальных уравнений для электропроводности, диффузии, теплопроводности и других параметров с соблюдением граничных условий для потенциальных функций на поверхностях раздела фаз. Этот способ расчета моделей назван нами потенциальным. Потенциальный способ расчета электропроводности моделей горных пород заключается в том, что путем решения дифференциальных уравнений Лапласа или Пуассона определяется распределение потенциальных полей в каждой из фаз горных пород. [27]

Представление информации физическими сигналами

Логические функции и логические элементы.

Основные понятия

Все цифровые вычислительные устройства построены на элементах, которые выполняют те или иные логические операции.

Для формального описания логической стороны процессов в цифровых устройствах используется алгебра логики (АЛ).

АЛ имеет дело с логическими переменными, которые могут принимать только два значения (ИСТИНА и ЛОЖЬ, TRUE и FALSE, ДА и НЕТ, 1 и 0). Наиболее распространено последнее обозначение. При этом 1 и 0 нельзя трактовать как числа, над ними нельзя производить арифметические действия.

Представление информации физическими сигналами.

Как уже говорилось, физическими аналогами логических переменных «0» и «1» служат сигналы, способные принимать два хорошо различимых состояния, например, потенциал низкого и высокого уровней, разомкнутое и замкнутое состояние контакта реле и т.п.

В схемах цифровых устройств (ЦУ) переменные и соответствующие им сигналы изменяются не непрерывно, а лишь в дискретные моменты, обозначаемые целыми неотрицательными числами: 0,1,2. i… Временной интервал между двумя соседними моментами дискретного времени называется тактом. Обычно ЦУ содержат специальный блок, вырабатывающий синхронизирующие сигналы, отмечающие моменты дискретного времени (границы тактов).

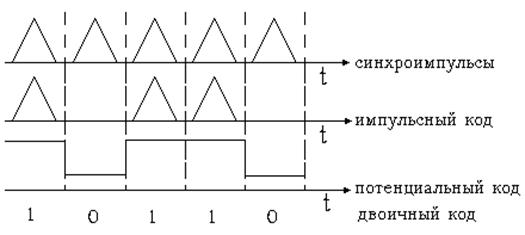

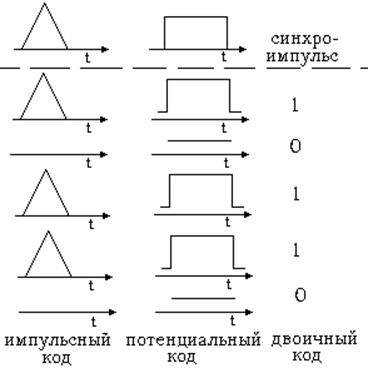

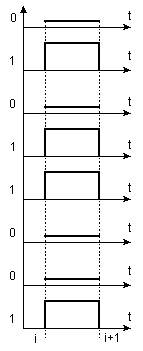

В современных ЦУ применяется потенциальный способ представления информации. Потенциальный сигнал сохраняет постоянный уровень в течение такта, а его значение в переходные моменты не является определенным (рис. 1.1)

Рис. 1.1. Представление цифровой информации сигналами потенциального типа (последовательный код).

При последовательном коде каждый временной такт предназначен для отображения одного разряда кода слова (рис. 1.1). В этом случае все разряды слова фиксируются по очереди одним и тем же элементом и проходят через одну линию передачи информации.

При параллельном коде все разряды двоичного слова представляются в одном временном такте, фиксируются отдельными элементами и проходят через отдельные линии, каждая из которых служит для представления и передачи только одного разряда слова. Код слова развертывается не во времени, а в пространстве, т.к. значения всех разрядов слова передаются по нескольким линиям одновременно (рис. 1.2).

Рис. 1.2. Представление информации параллельным кодом.

Логические функции.

Как бы ни была сложна логическая связь между логической функцией и ее аргументами, эту связь всегда можно представить в виде совокупности трех простейших логических операций: НЕ, И, ИЛИ. Этот набор называют булевским базисом, в честь английского математика Д.Буля (1815-1864), разработавшего основные положения АЛ.

Электронный логический элемент (ЛЭ), реализующий функцию НЕ в виде определенных уровней напряжения, называют инвертором. Инвертор на схемах изображается, как показано на рис. 1.3,а. Вход- слева, выход- справа, кружок- символ инверсии. Условное изображение инвертора (или любого другого ЛЭ) на схеме может быть повернуто на 90° (вход- сверху, выход- снизу, рис. 1.3,б). Другие углы поворота и направления входов и выходов не допускаются.

В релейно-контактной технике функцию НЕ реализует нормально замкнутый контакт (рис. 1.3,в), т.е. такой контакт реле, который замкнут, пока в обмотке нет токового сигнала

а) предпочтительное изображение

б) допустимое изображение

в) реализация НЕ в релейно-контактной технике

Функция И (другие названия: конъюнкция, логическое умножение, AND)- это функция двух или большего числа аргументов.

Функция И равна 1 тогда и только тогда, когда все ее аргументы равны 1. В релейно-контактной технике функция И реализуется последовательным включением нормально разомкнутых контактов (рис. 1.4,а). Ток в цепи пойдет, когда контакты замкнуты, т.е. находятся в единичном состоянии.

Значения функции И для всех комбинаций аргументов a и b приведены в таблице 1.1. Там же приведены значения и других часто используемых функций, о которых речь будет вестись ниже.

Элемент, реализующий функцию И, называют элемент И или конъюнктор. Элемент И часто используют для управления потоком информации. При этом на один его вход поступают логические сигналы, несущие некоторую информацию, а на другой- управляющий сигнал: пропускать- 1, не пропускать-0. Элемент И, используемый таким образом, называют вентиль (gate).

| Аргументы | Функции | ||||||

| а | b | И | ИЛИ | И-НЕ | ИЛИ-НЕ | М2 | º |

Функцию И можно построить от любого числа аргументов. На рис. 1.2,б и в показаны условные изображения двух- и четырехвходового конъюнкторов.

а) реализация операции И на контактах реле

б) условное изображение двухвходового конъюнктора 2И (AND2)

в) то же для четырехвходового- 4И (AND4)

Функция ИЛИ (другие названия: дизъюнкция, логическое сложение, OR)- это функция двух или большего числа аргументов. Функция ИЛИ равна 1, если хотя бы один из ее аргументов равен 1. Обозначение: Q=aÚ b, Q=a+b. Читается: «Q есть a или b». Использовать знак «плюс» можно в тех случаях, когда дизъюнкцию нельзя смешать с арифметическим суммированием и сложением по модулю 2.

Условное изображение трехвходового дизъюнктора (3ИЛИ, OR3) показано на рис. 1.5,а. В релейно-контактных схем ах функция ИЛИ реализуется параллельным включением контактов (рис. 1.5,б)

а) условное изображение

б) реализация ИЛИ на контактах

Законы алгебры логики

АЛ базируется на нескольких аксиомах, из которых выводят основные законы для преобразований с логическими переменными. Каждая аксиома представлена в двух видах, что вытекает из принципа дуальности логических операций, согласно которому операции конъюнкции и дизъюнкции допускают взаимную замену, если одновременно поменять 1 на 0, 0 на 1, знак Ú на ×, а знак × на Ú.

Аксиомы операции отрицания:

Аксиомы операций конъюнкции и дизъюнкции:

2а) 1×0=0×1=0 2б) 0Ú1=1Ú0=1

Законы АЛ вытекают из аксиом и также имеют две формы выражения а) и б).

1. Переместительный закон

2. Сочетательный закон

3. Закон тавтологии

4. Закон обращения: если a=b, то

5. Закон двойной инверсии:

6. Закон нулевого множества

7. Закон универсальногомножества

8. Закон дополнительности

а) a×

9. Распределительный закон

10. Закон поглощения

11. Закон склеивания

а) (aÚb)(aÚ

12. Закон инверсии (закон Де Моргана)

а)

или после инвертирования

в)

Представление информации физическими сигналами

Страницы работы

Содержание работы

Представление информации физическими сигналами.

Сигналы в ЦВМ принято подразделять на два вида: потенциальные и импульсные.

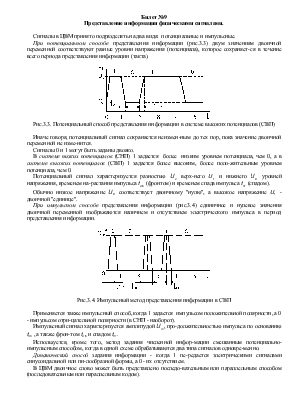

При потенциальном способе представления информации (рис.3.3) двум значениям двоичной переменной соответствуют разные уровни напряжения (потенциала), которое сохраняет-ся в течение всего периода представления информации (такта).

Рис.3.3. Потенциальный способ представления информации в системе высоких потенциалов (СВП)

Иначе говоря, потенциальный сигнал сохраняется неизмен-ным до тех пор, пока значение двоичной переменной не изме-нится.

Сигналы 0 и 1 могут быть заданы двояко.

В системе низких потенциалов (СНП) 1 задается более низким уровнем потенциала, чем 0, а в системе высоких потенциалов (СВП) 1 задается более высоким, более поло-жительным уровнем потенциала, чем 0.

Потенциальный сигнал характеризуется разностью

Обычно низкое напряжение

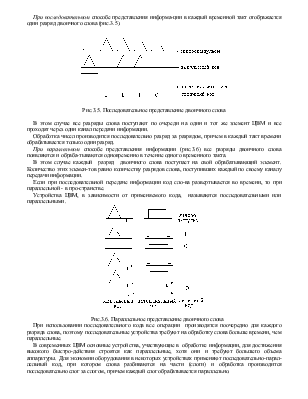

При импульсном способе представления информации (рис.3.4) единичное и нулевое значения двоичной переменной изображаются наличием и отсутствием электрического импульса в период представления информации.

Рис.3.4. Импульсный метод представления информации в СВП

Импульсный сигнал характеризуется амплитудой

Используется, кроме того, метод задания численной инфор-мации смешанным потенциально-импульсным способом, когда в одной схеме обрабатываются два типа сигналов одновре-менно.

В ЦВМ двоичное слово может быть представлено последо-вательным или параллельным способом (последовательным или параллельным кодом).

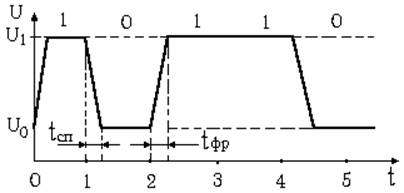

При последовательном способе представления информа-ции в каждый временной такт отображается один разряд двоичного слова (рис.3.5).

Рис.3.5. Последовательное представление двоичного слова

В этом случае все разряды слова поступают по очереди на один и тот же элемент ЦВМ и все проходят через один канал передачи информации.

Обработка чисел производится последовательно разряд за разрядом, причем в каждый такт времени обрабатывается только один разряд.

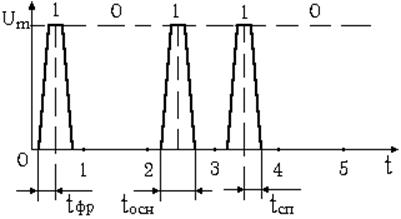

При параллельном способе представления информации (рис.3.6) все разряды двоичного слова появляются и обраба-тываются одновременно в течение одного временного такта.

В этом случае каждый разряд двоичного слова поступает на свой обрабатывающий элемент. Количество этих элемен-тов равно количеству разрядов слова, поступивших каждый по своему каналу передачи информации.

Устройства ЦВМ, в зависимости от применяемого кода, называются последовательными или параллельными.

Рис.3.6. Параллельное представление двоичного слова

При использовании последовательного кода все операции производятся поочередно для каждого разряда слова, поэтому последовательные устройства требуют на обработку слова больше времени, чем параллельные.

В современных ЦВМ основные устройства, участвующие в обработке информации, для достижения высокого быстро-действия строятся как параллельные, хотя они и требуют большего объема аппаратуры. Для экономии оборудования в некоторых устройствах применяют последовательно-парал-лельный код, при котором слова разбиваются на части (слоги) и обработка производится последовательно слог за слогом, причем каждый слог обрабатывается параллельно.

Что такое потенциальный способ представления логических переменных

Осн. функциональными типами П. л. э. являются схемы совпадения (схемы «И»), схемы разделения (схемы «ИЛИ») и инверторы (схемы «НЕ») потенциальных сигналов. Эти схемы выполняются в виде отдельных элементов и в виде типовых сочетаний. Широко распространенными сочетаниями служат схемы с активным выходом «И-НЕ», «ИЛИ-НЕ», «И-ИЛИ-НЕ», каждая из которых реализует универсальный логический элемент ЦВМ (см. Дискретных элементов система).

Классификационный перечень П. л. э. по типу компонентов весьма разнообразен. Обычно в интегральном исполнении чаще всего используются П. л. э. диодно-транзисторной логики (схемы ДТЛ), транзисторно-транзистор-ной логики (схемы ТТЛ), резисторно-транзисторной логики (схемы РТЛ; их вариант, приведенный на рис., наз. также схемами МТЛНС, т. е. модифицированной транзисторной логики с непосредственными связями) и транзисторной логики с эмиттерными связями (схемы ТЛЭС). На рис. приведены характерные примеры этих схем, выполняющих логические функции

Недостатком схем РТЛ являются низкие значения коэфф. разветвления и помехоустойчивости. Схемы ДТЛ труднее изготовить, но они позволяют достичь хорошего компромисса между такими параметрами, как задержка распространения сигнала, нагрузочная способность, помехоустойчивость и потребляемая мощность. Схемы ТТЛ являются развитием схем ДТЛ в том смысле, что для них входная цепь

Недостаток их — меньший коэфф. разветвления по входу. Еще большее быстродействие схем ТЛЭС, в которых транзисторы не входят в насыщение, в отличие от рассмотренных выше схем, где возникают задержки из-за насыщения транзисторов. В схемах ТЛЭС используют принцип переключения токов при малых изменениях входных напряжений. Недостаток ТЛЭС — повышенная потребляемость мощности и низкая помехоустойчивость.

Схемы потенциальных логических элементов: а — диодно-транзисторной логики; б — транзисторно-транзисторной логики; в — резисторно-транзисторной логики; г — транзисторной логики с эмиттерными связями.

Характерными отечественными комплексами П. л. э. из числа получивших наибольшее внедрение являются системы: «Урал-10», «МИР-1» (обе на основе схем ДТЛ), элементы «БЭСМ-6» (на основе схем ТЛЭС), «Тропа» (на основе схем РТЛ) и некоторые другие. Комплекс «Урал-10» (как и «МИР-1») включает осн. универсальный логический элемент «И-НЕ»-модули А, Б и Г (их время переключения составляет соответственно 0,25, 0,63 и 6,3 мксек) и модули трех других типов. Элементы «БЭСМ-6» за счет эффекта токового переключения обеспечивают время переключения осн. элемента около 30 нсек, причем при нагрузке 6—8 модулей это время не превышает 50 нсек. Кроме осн. элемента, которым является быстродействующий усилитель—переключатель тока с диодной логикой на входе, в данной системе есть и отдельные диодные логические схемы, спец. усилитель для работы на высокочастотный кабель и ячейка световой индикации. Для уменьшения длины связей используют

платы с двусторонним монтажом. Комплекс П. л. э. «Тропа» составлен из шести интегральных схем типа универсального логического элемента с возможностями подключения дополнительно не более шести входов для образования логических функций «И» либо «ИЛИ». Для данных П. л. э. задержка составляет величину порядка 40 нсек, мощность рассеивания 11-26 мет, нагрузочная способность 2-8.

Интенсивно развиваются П. л. э. на основе интегральных схем ТТЛ, позволяющие значительно улучшить большинство тех. параметров. Дальнейшие перспективы улучшения рабочих параметров П. л. э. и снижение стоимости реализации во многом связаны с повышением уровня их интеграции. См. также Потенциальная элементная структура ЦВМ.

Лит.: Петров В. П. Проектирование цифровых систем контроля и управления, м., 1967; Шигин А. Г. Цифровые вычислительные машины (элементы и узлы). М., 1971 [библиогр. с. 315—317].

ПОТЕНЦИАЛЬНЫЕ ЛОГИЧЕКИЕ ЭЛЕМЕНТЫ

4.1 Потенциальные логические элементы (ПЛЭ). Типы,

характеристики и параметры

В настоящее время при разработке интегральных схем (ИС) наибольшее распространение получили следующие типы логических элементов:

— транзисторно-транзисторная логика (ТТЛ);

— эмиттерно-связанная логика (ЭСЛ);

— интегрально-инжекторная логика (И2Л);

— диодно-транзисторная логика (ДТЛ);

— логика на однотипных полевых транзисторах (n-МОП и p-МОП);

— логика на комплиментарных полевых транзисторах;

Самым распространёнными на сегодняшний день являются ИС, реализующие ТТЛ и её разновидности. Интегральные схемы данного типа обладают средним быстродействием (

На рисунках 4.1 – 4.7 представлены графические обозначения и выполняемые функции потенциальных логических элементов.

Рисунок 4.1 — Инвертор Рисунок 4.1 — Инвертор  |  Рисунок 4.2 — Повторитель Рисунок 4.2 — Повторитель  |

Рисунок 4.3 — Рисунок 4.3 —  |  Рисунок 4.4 — Рисунок 4.4 —  |

Рисунок 4.5 — Рисунок 4.5 —  |  Рисунок 4.6 — Рисунок 4.6 —  |

Рисунок 4.7 — Сумматор по mod2 Рисунок 4.7 — Сумматор по mod2  |

Логические элементы ТТЛ типа.

Различают элементы с положительной (транзистор типа n-p-n) и отрицательной логикой (транзистор типа p-n-p). В положительной логике значению логической «1» ставят в соответствие большее, а значению логического «0» – меньшее значение напряжения или тока. В отрицательной логике наоборот – большим значениям электрического сигнала соответствуют значения логического «0», меньшим – значения логической «1». Это определение справедливо для любой полярности используемого напряжения или любых направлениях токов. Важно отметить, что если некоторое логическое устройство относительно положительной логики реализует операцию «И», то относительно отрицательной логики это будет операция «ИЛИ» и наоборот.

Потенциальный способ представления логического «0» и логической «1» при положительной логике приведен на рис. 4.8.

|  — уровень логического «0»; — уровень логического «0»;  — уровень логической «1»; — уровень логической «1»;  . . |

| Рисунок 4.8 — Представление положительной логики |

Потенциальный способ представления логического «0» и логической «1» при отрицательной логике приведен на рис 4.9.

|  — уровень логической «1»; — уровень логической «1»;  — уровень логического «0»; — уровень логического «0»;  . . |

| Рисунок 4.9 — Представление отрицательной логики |

Динамические характеристики ПЛЭ приведены на рис. 4.10

Рисунок 4.10 — Динамические характеристики ПЛЭ

Время задержки ПЛЭ зависит от времени задержки переднего

Нагрузочная способность ЛЭ характеризует его способность получать сигнал от нескольких источников информации и одновременно быть источником информации для ряда других элементов. Для численной характеристики нагрузочной способности ЛЭ используются два коэффициента: m-коэффициент разветвления и n-коэффициент объединения.

1) m-коэффициент разветвления – характеризует количество входов для элементов данной серии, которое допускается для подключения к выходу данного элемента.

2) n-коэффициент объединения – характеризуется количеством входов данного логического элемента (от двух и более)

Различают статические характеристики ПЛЭ.

1)

2)

Рисунок 4.11 — Нагрузочная характеристика ЛЭ

3)

Рисунок 4.12 — Амплитудная передаточная характеристика инвертирующего ПЛЭ ТТЛ-типа с положительной логикой

Рисунок 4.13 — Амплитудная передаточная характеристика неинвертирующего ПЛЭ ТТЛ-типа с положительной логикой

Логическая «1» соответствует уровням от

Логический «0» соответствует уровням от

Участок АВ — соответствует зоне отсечки ключа, CD — насыщению, ВС — переходная область (активный режим,

Помехоустойчивость ЛЭ при передаче «0» на входе

Помехоустойчивость ЛЭ при передаче «1» определяется аналогично:

Помехоустойчивость ЛЭ определяет максимально возможное значение аддитивной помехи на входе ЛЭ, которое не приводит к переключению элемента в другое состояние (или неопределённое). Помехоустойчивости

Рисунок 4.14 — Помехоустойчивость ЛЭ

Повышение запаса помехоустойчивости достигается увеличением

Быстродействие ЛЭ серий ИС ТТЛ в основном определяется инерционными свойствами применяемых биполярных транзисторов и нагрузки. Инерционность, обусловленная параметрами нагрузки, зависит от конкретной схемы и конструктивного выполнения логического устройства. Инерционность, связанная с собственно частотными свойствами ЛЭ, может быть уменьшена изменением схемотехники и режимов работы самого элемента. Основными причинами инерционности транзисторных ключей на биполярных транзисторах являются перезаряд его коллекторной ёмкости и время рассасывания. Эти параметры определяются как технологией изготовления транзисторов, так и режимами их работы в ключевой схеме. В частности, уменьшение длительностей переключения, обусловленных перезарядом коллекторной ёмкости при её неизменном значении, можно добиться уменьшением сопротивления коллекторной нагрузки.

Применяемые отечественные серии ПЛЭ:

К155, К154 — базовыми элементами являются биполярные транзисторы;

К156 — полевые транзисторы;

Л – наименование логических элементов;

Б – характер группы данного класса;

И – серия схем совпадения («И»);

Н – элемент отрицания;

П – прочие элементы;

1 – номер разработки данного класса.

Логические элементы бывают трёх видов:

1) потенциальные (гальванические) связи в элементах без конденсаторов;

2) импульсные – связи через конденсаторы С или через импульсные трансформаторы;

3) потенциально-импульсные, в которых имеет место и первый, и второй вид связей.

Диодная логика (ДЛ)

Логика «И»

Принципиальная схема простейшего логического элемента «И» и таблица истинности представлены на рис. 4.15. Если хотя бы на одном входе схемы имеется низкий уровень положительного напряжения, принимаемый за условный нуль, то диод, связанный через катод с этим входом, открыт и напряжение на его аноде, а, следовательно, и на выходе устройства равно нулю. Если же на всех входах схемы присутствует высокий (единичный) уровень напряжения, то выходной сигнал равен единице.

Логика «ИЛИ»

| Таблица 4.1

| |||

| Рисунок 4.15 — ДЛ типа «И» с таблицей истинности |

| Таблица 4.2

| |||

| Рисунок 4.16 — ДЛ типа «ИЛИ» с таблицей истинности |

Недостатки диодной логики: схемы критичны к внутреннему сопротивлению источников ЭДС (

Время задержки

Для ликвидации указанных недостатков были разработаны схемы ДТЛ (диодно-транзисторная логика).