Что такое регенерация ram

В динамических ОЗУ чаще используется т.н. «строчная регенерация», при которой в одном цикле регенерируются все элементы, расположенные в одной строке прямоугольной матрицы накопителя. Следует отметить, что любое обращение к запоминающей ячейке (запись или чтение) осуществляет ее регенерацию и одновременно регенерирует все ячейки, расположенные в той же строке накопителя.

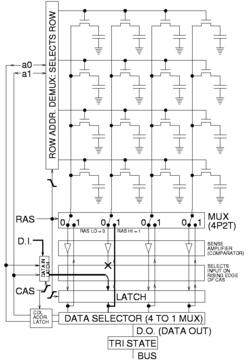

Рис. 1. Управление регенерацией динамической памяти

Различают несколько способов организации регенерации динамических ОЗУ в МПС.

Регенерация «по таймеру». В состав М ПС вкл ючается таймер регенерации, который каждые 2 мС формирует сигнал, блокирующий обращение МП к памяти и запускающий процедуру регенерации. Схема управления регенерацией включает в себя счетчик адреса регенерации, триггер регенерации и мультиплексор адреса.

Так, в машинном цикле МП i8080 могут появляться такты T4, T5, в которых МП не занимает системную шину. Эти моменты времени можно выделять специальной схемой и использовать для регенерации.

Микропроцессор Z80 имеет встроенный счетчик регенерации и обеспечивает этот процесс самостоятельно параллельно с внутренней обработкой информации на кристалле.

БИС динамических ЗУ имеют объемы от 16К ´ 1 (565РУ3) до 1М ´ 1 (..РУ 9 ), но имеют одинаковую структуру и линии управления (за исключением числа адресных).

Из рисунков следует, что адрес ячейки подается в ОЗУ последовательно двумя порциями по одним и тем же линиям в сопровождении управляющих сигналов RAS\ (строб адреса строки) и CAS\ (строб адреса столбца). Поэтому адрес на системной шине, формируемый МП, должен мультиплексироваться, одновременно вырабатываться управляющие сигналы RAS и CAS.

Кристалл ОЗУ бывает выбран только при условии RAS = CAS = 0, что позволяет осуществлять селекцию блоков по двум координатам.

Контроллер динамической памяти (КДП) обеспечивает мультиплексирование адреса системной шины, выработку управляющих сигналов CAS и RAS[3:0] (для селекции модулей ОЗУ), а также внутреннюю (по таймеру) или внешнюю (прозрачную) регенерацию.

Структурная схема контроллера включает в себя :

· буферные схемы Буф.1,2,3 для подключения системной шины адреса и управления;

· счетчик адреса регенерации;

· схему управления с тактовым генератором, таймером и триггером регенерации, арбитром и логической схемой L для формирования управляющих сигналов.

Рис. 4. Контроллер динамического ОЗУ

Выходной сигнал SACK\ вырабатывается КДП в начале цикла обращения к памяти. Если запрос от МП приходится на цикл регенерации, то SACK\ задерживается до начала цикла чтения/записи.

Выходной сигнал XACK\ («Готовность данных») вырабатывается в конце цикла чтения/записи.

Сигналы SACK\ и XACK\ можно использовать для управления потенциалом на входе READY микропроцессора.

Что такое регенерация ram

DRAM (Dynamic random access memory, Динамическая память с произвольным доступом) — тип энергозависимой полупроводниковой памяти с произвольным доступом; DRAM широко используемая в качестве оперативной памяти современных компьютеров, а также в качестве постоянного хранилища информации в системах, требовательных к задержкам.

Физически DRAM состоит из ячеек, созданных в полупроводниковом материале, в каждой из которых можно хранить определённый объём данных, строку от 1 до 4 бит. Совокупность ячеек такой памяти образуют условный «прямоугольник», состоящий из определённого количества строк и столбцов. Один такой «прямоугольник» называется страницей, а совокупность страниц называется банком. Весь набор ячеек условно делится на несколько областей.

Как запоминающее устройство, DRAM представляет собой модуль памяти различных конструктивов, состоящий из электрической платы, на которой расположены микросхемы памяти и разъёма, необходимого для подключения модуля к материнской плате.

Содержание

Принцип действия

Физически DRAM-память представляет собой набор запоминающих ячеек, которые состоят из конденсаторов и транзисторов, расположенных внутри полупроводниковых микросхем памяти. [1]

При отсутствии подачи электроэнергии к памяти этого типа происходит разряд конденсаторов, и память опустошается (обнуляется). Для поддержания необходимого напряжения на обкладках конденсаторов ячеек и сохранения их содержимого, их необходимо периодически подзаряжать, прилагая к ним напряжения через коммутирующие транзисторные ключи. Такое динамическое поддержание заряда конденсатора является основополагающим принципом работы памяти типа DRAM. Конденсаторы заряжают в случае, когда в «ячейку» записывается единичный бит, и разряжают в случае, когда в «ячейку» необходимо записать нулевой бит.

Важным элементом памяти этого типа является чувствительный усилитель-компаратор (англ. sense amp ), подключенный к каждому из столбцов «прямоугольника». Он, реагируя на слабый поток электронов, устремившихся через открытые транзисторы с обкладок конденсаторов, считывает всю строку целиком. Именно строка является минимальной порцией обмена с динамической памятью, поэтому обмен данными с отдельно взятой ячейкой невозможен.

Регенерация

В отличие от быстрой, но дорогой статической памяти типа SRAM (англ. static random access memory ), которая является конструктивно более сложным и более дорогим типом памяти и используется в основном в кэш-памяти, медленная, но дешёвая память DRAM изготавливается на основе конденсаторов небольшой ёмкости, которые быстро теряют заряд, поэтому информацию приходится обновлять через определённые промежутки времени во избежание потерь данных. Этот процесс называется регенерацией памяти. Он реализуется специальным контроллером, установленным на материнской плате или же на кристалле центрального процессора. На протяжении времени, называемого шагом регенерации, в DRAM перезаписывается целая строка ячеек, и через 8-64 мс обновляются все строки памяти.

Процесс регенерации памяти в классическом варианте существенно тормозит работу системы, поскольку в это время обмен данными с памятью невозможен. Регенерация, основанная на обычном переборе строк, в современных типах DRAM не применяется. Существует несколько более экономичных вариантов этого процесса — расширенный, пакетный, распределённый; наиболее экономичной является скрытая (теневая) регенерация.

Среди новых технологий регенерации — PASR (англ. Partial Array Self Refresh ), применяемый компанией Samsung в чипах памяти SDRAM с низким уровнем энергопотребления. Регенерация ячеек выполняется только в период ожидания в тех банках памяти, в которых имеются данные.

Параллельно с этой технологией реализуется метод TCSR (англ. Temperature Compensated Self Refresh ), который предназначен для регулировки скорости процесса регенерации в зависимости от рабочей температуры.

Характеристики памяти DRAM

Основными характеристиками DRAM являются рабочая частота и тайминги.

При обращении к ячейке памяти контроллер памяти задаёт номер банка, номер страницы в нём, номер строки и номер столбца и на все эти запросы тратится время, помимо этого довольно большой период уходит на открытие и закрытие банка после самой операции. На каждое действие требуется время, называемое таймингом.

Основными таймингами DRAM являются: задержка между подачей номера строки и номера столбца, называемая временем полного доступа (англ. RAS to CAS delay ), задержка между подачей номера столбца и получением содержимого ячейки, называемая временем рабочего цикла (англ. CAS delay ), задержка между чтением последней ячейки и подачей номера новой строки (англ. RAS precharge ). Тайминги измеряются в наносекундах или тактах, и чем меньше величина этих таймингов, тем быстрее работает оперативная память.

Типы DRAM

На протяжении долгого времени разработчиками создавались различные типы памяти. Они обладали разными характеристиками, в них были использованы разные технические решения. Основной движущей силой развития памяти было развитие компьютеров и центральных процессоров. Постоянно требовалось увеличение быстродействия и объёма оперативной памяти.

Страничная память

Страничная память (англ. page mode DRAM, PM DRAM ) являлась одним из первых типов выпускаемой компьютерной оперативной памяти. Память такого типа выпускалась в начале 1990-х годов, но с ростом производительности процессоров и ресурсоёмкости приложений требовалось увеличивать не только объём памяти, но и скорость её работы.

Быстрая страничная память

Быстрая страничная память (англ. fast page mode DRAM, FPM DRAM ) появилась в 1995 году. Принципиально новых изменений память не претерпела, а увеличение скорости работы достигалось путём повышенной нагрузки на аппаратную часть памяти. Данный тип памяти в основном применялся для компьютеров с процессорами Intel 80486 или аналогичных процессоров других фирм. Память могла работать на частотах 25 и 33 МГц с временем полного доступа 70 и 60 нс и с временем рабочего цикла 40 и 35 нс соответственно.

EDO DRAM — память с усовершенствованным выходом

C появлением процессоров Intel Pentium память FPM DRAM оказалась совершенно неэффективной. Поэтому следующим шагом стала память с усовершенствованным выходом (англ. extended data out DRAM, EDO DRAM ). Эта память появилась на рынке в 1996 году и стала активно использоваться на компьютерах с процессорами Intel Pentium и выше. Её производительность оказалась на 10-15 % выше по сравнению с памятью типа FPM DRAM. Её рабочая частота была 40 и 50 МГц, соответственно, время полного доступа — 60 и 50 нс, а время рабочего цикла — 25 и 20 нс. Эта память содержит регистр-защелку (англ. data latch ) выходных данных, что обеспечивает некоторую конвейеризацию работы для повышения производительности при чтении.

SDR SDRAM — синхронная DRAM

В связи с выпуском новых процессоров и постепенным увеличением частоты системной шины, стабильность работы памяти типа EDO DRAM стала заметно падать. Ей на смену пришла синхронная память — Single Data Rate Synchronous Dynamic Random Access Memory (SDR SDRAM). Новыми особенностями этого типа памяти являлись использование тактового генератора для синхронизации всех сигналов и использование конвейерной обработки информации. Также память надёжно работала на более высоких частотах системной шины (100 МГц и выше).

Если для FPM и EDO памяти указывается время чтения первой ячейки в цепочке (время доступа), то для SDRAM указывается время считывания последующих ячеек. Цепочка — несколько последовательных ячеек. На считывание первой ячейки уходит довольно много времени (60-70 нс) независимо от типа памяти, а вот время чтения последующих сильно зависит от типа. Рабочие частоты этого типа памяти могли равняться 66, 100 или 133 МГц, время полного доступа — 40 и 30 нс, а время рабочего цикла — 10 и 7,5 нс.

С этим типом памяти применялась технология Virtual Channel Memory (VCM). VCM использует архитектуру виртуального канала, позволяющую более гибко и эффективно передавать данные с использованием каналов регистра на чипе. Данная архитектура интегрирована в SDRAM. VCM, помимо высокой скорости передачи данных, была совместима с существующими SDRAM, что позволяло делать апгрейд системы без значительных затрат и модификаций. Это решение нашло поддержку у некоторых производителей чипсетов.

Enhanced SDRAM (ESDRAM)

Для преодоления некоторых проблем с задержкой сигнала, присущих стандартной DRAM-памяти, было решено встроить небольшое количество SRAM в чип, то есть создать на чипе кеш.

ESDRAM — это, по существу, SDRAM с небольшим количеством SRAM. При малой задержке и пакетной работе достигается частота до 200 МГц. Как и в случае внешней кеш-памяти, SRAM-кеш предназначен для хранения и выборки наиболее часто используемых данных. Отсюда и уменьшение времени доступа к данным медленной DRAM.

Одним из таких решений являлась ESDRAM от Ramtron International Corporation.

Пакетная EDO RAM

Пакетная память EDO RAM (англ. burst extended data output DRAM, BEDO DRAM ) стала дешёвой альтернативой памяти типа SDRAM. Основанная на памяти EDO DRAM, её ключевой особенностью являлась технология поблочного чтения данных (блок данных читался за один такт), что сделало её работу быстрее, чем у памяти типа SDRAM. Однако невозможность работать на частоте системной шины более 66 МГц не позволила данному типу памяти стать популярным.

Video RAM

Специальный тип оперативной памяти — Video RAM (VRAM) — был разработан на основе памяти типа SDRAM для использования в видеоплатах. Он позволял обеспечить непрерывный поток данных в процессе обновления изображения, что было необходимо для реализации изображений высокого качества. На основе памяти типа VRAM, появилась спецификация памяти типа Windows RAM (WRAM), иногда её ошибочно связывают с операционными системами семейства Windows. Её производительность стала на 25 % выше, чем у оригинальной памяти типа SDRAM, благодаря некоторым техническим изменениям.

DDR SDRAM

У всех предыдущих DRAM были разделены линии адреса, данных и управления, которые накладывают ограничения на скорость работы устройств. Для преодоления этого ограничения в некоторых технологических решениях все сигналы стали выполняться на одной шине. Двумя из таких решений являются технологии DRDRAM и SLDRAM. Они получили наибольшую популярность и заслуживают внимания. Стандарт SLDRAM является открытым и, подобно предыдущей технологии, SLDRAM использует оба перепада тактового сигнала. Что касается интерфейса, то SLDRAM перенимает протокол, названный SynchLink Interface и стремится работать на частоте 400 МГц.

Память DDR SDRAM работает на частотах в 100, 133, 166 и 200 МГц, её время полного доступа — 30 и 22,5 нс, а время рабочего цикла — 5, 3,75, 3 и 2,5 нс.

Так как частота синхронизации лежит в пределах от 100 до 200 МГц, а данные передаются по 2 бита на один синхроимпульс, как по фронту, так и по срезу тактового импульса, то эффективная частота передачи данных лежит в пределах от 200 до 400 МГц. Такие модули памяти обозначаются DDR200, DDR266, DDR333, DDR400.

Direct RDRAM или Direct Rambus DRAM

Тип памяти RDRAM является разработкой компании Rambus. Высокое быстродействие этой памяти достигается рядом особенностей, не встречающихся в других типах памяти. Первоначальная очень высокая стоимость памяти RDRAM привела к тому, что производители мощных компьютеров предпочли менее производительную, зато более дешёвую память DDR SDRAM. Рабочие частоты памяти — 400, 600 и 800 МГц, время полного доступа — до 30 нс, время рабочего цикла — до 2,5 нс.

DDR2 SDRAM

Конструктивно новый тип оперативной памяти DDR2 SDRAM был выпущен в 2004 году. Основываясь на технологии DDR SDRAM, этот тип памяти за счёт технических изменений показывает более высокое быстродействие и предназначен для использования на современных компьютерах. Память может работать с тактовой частотой шины 200, 266, 333, 337, 400, 533, 575 и 600 МГц. При этом эффективная частота передачи данных соответственно будет 400, 533, 667, 675, 800, 1066, 1150 и 1200 МГц. Некоторые производители модулей памяти помимо стандартных частот выпускают и образцы, работающие на нестандартных (промежуточных) частотах. Они предназначены для использования в разогнанных системах, где требуется запас по частоте. Время полного доступа — 25, 11,25, 9, 7,5 нс и менее. Время рабочего цикла — от 5 до 1,67 нс.

DDR3 SDRAM

Этот тип памяти основан на технологиях DDR2 SDRAM со вдвое увеличенной частотой передачи данных по шине памяти. Отличается пониженным энергопотреблением по сравнению с предшественниками. Частота полосы пропускания лежит в пределах от 800 до 2400 МГц (рекорд частоты — более 3000 МГц), что обеспечивает большую пропускную способность по сравнению со всеми предшественниками.

Динамическая оперативная память

Динамическая оперативная память (DRAM – Dynamic Random Access Memory) – энергозависимая полупроводниковая память с произвольным доступом. На данный момент – это основной тип оперативной памяти, используемый в современных персональных компьютерах и обеспечивающий наилучший показатель отношения цена-качество по сравнению с другими типами оперативной памяти. Однако, требования к быстродействию, энергопотреблению и надежности оперативной памяти постоянно растут, и динамическая оперативная память уже с трудом соответствует современным потребностям, так что в ближайшие годы стоит ожидать появления серийно выпускаемых конкурирующих типов оперативной памяти, таких как магниторезистивная оперативная память.

Содержание.

1. Устройство динамической оперативной памяти.

Динамическая оперативная память (DRAM – Dynamic Random Access Memory) – энергозависимая память с произвольным доступом, каждая ячейка которой состоит из одного конденсатора и нескольких транзисторов. Конденсатор хранит один бит данных, а транзисторы играют роль ключей, удерживающих заряд в конденсаторе и разрешающих доступ к конденсатору при чтении и записи данных.

Однако транзисторы и конденсатор – неидеальные, и на практике заряд с конденсатора достаточно быстро истекает. Поэтому периодически, несколько десятков раз в секунду, приходится дозаряжать конденсатор. К тому же процесс чтения данных из динамической памяти – деструктивен, то есть при чтении конденсатор разряжается, и необходимо его заново подзаряжать, чтобы не потерять навсегда данные, хранящиеся в ячейке памяти.

На практике существуют разные способы реализации динамической памяти. Упрощенная структурная схема одного из способов реализации приведена на рисунке 1.

Как видно из рисунка, основным блоком памяти является матрица памяти, состоящая из множества ячеек, каждая из которых хранит 1 бит информации.

Каждая ячейка состоит из одного конденсатора (С) и трех транзисторов. Транзистор VT1 разрешает или запрещает запись новых данных или регенерацию ячейки. Транзистор VT3 выполняет роль ключа, удерживающего конденсатор от разряда и разрешающего или запрещающего чтение данных из ячейки памяти. Транзистор VT2 используется для считывания данных с конденсатора. Если на конденсаторе есть заряд, то транзистор VT2 открыт, и ток пойдет по линии AB, соответственно, на выходе Q1 тока не будет, что означает – ячейка хранит бит информации с нулевым значением. Если заряда на конденсаторе нет, то конденсатор VT2 закрыт, а ток пойдет по линии AE, соответственно, на выходе Q1 ток будет, что означает – ячейка хранит бит информации со значением “единица”.

Заряд в конденсаторе, используемый для поддержания транзистора VT2 в открытом состоянии, во время прохождения по нему тока, быстро расходуется, поэтому при чтении данных из ячейки необходимо проводить регенерацию заряда конденсатора.

Для работы динамической памяти на матрицу должно всегда поступать напряжение, на схеме оно обозначено, как Uп. С помощью резисторов R напряжение питания Uп равномерно распределяется между всеми столбцами матрицы.

Также в состав памяти входит контроллер шины памяти, который получает команды, адрес и данные от внешних устройств и ретранслирует их во внутренние блоки памяти.

Команды передаются в блок управления, который организует работу остальных блоков и периодическую регенерацию ячеек памяти.

Адрес преобразуется в две составляющие – адрес строки и адрес столбца, и передается в соответствующие дешифраторы.

Дешифратор адреса строки определяет, с какой строки надо провести чтение или запись, и выдает на эту строку напряжение.

Дешифратор адреса столбца при чтении данных определяет, какие из считанных бит данных были запрошены и должны быть выданы в шину памяти. При записи данных дешифратор определяет, в какие столбцы надо подать команды записи.

Блок работы с данными определяет, какие данные, в какую ячейку памяти требуется записать, и выдает соответствующие биты данных для записи в эти ячейки.

Блоки регенерации определяют:

Буфер данных сохраняет всю считанную строку матрицы, так как при чтении всегда считывается вся строка целиком, и позволяет потом выбрать из считанной строки требуемые биты данных.

Рассмотрим принцип работы динамической памяти на примере структурной схемы, приведенной на рисунке 1. Рассматривать будем работу с первой ячейкой (M11). Работа остальных ячеек памяти полностью идентична.

1.1. Работа динамической памяти в состоянии покоя.

И так, первое что мы рассмотрим – этот состояние покоя, когда к памяти отсутствуют обращения, и она не в стадии регенерации данных.

DRAM – память энергозависимая, поэтому работа с ней возможна только при подаче питания. На схеме подаваемое на плату питание обозначено, как Uп. Подаваемое питание распределяется между всеми столбцами матрицы памяти с помощью транзисторов R.

Если память бездействует (от контроллера шины памяти не приходит никаких команд), то от дешифратора адреса строки не выдается сигнал ни на одну линию строк (S1-Sn) матрицы памяти. Соответственно, транзисторы VT1 и VT3 ячейки памяти M11 закрыты, также как и аналогичные транзисторы всех остальных ячеек памяти.

Следовательно, ток от подаваемого питания проходит по линии AE для первого столбца и аналогично для всех остальных столбцов матрицы памяти. Далее попадает на выходы Q1-Qm, на которых устанавливается «высокий» уровень напряжения, соответствующий значению логической «1». Но так как никаких команд от блока управления нет, то «Буфер данных» игнорирует получаемые сигналы.

Тут становится понятно, зачем нужен транзистор VT3. Он защищает конденсатор от разряда, когда к данной ячейки памяти нет обращения.

Ток по линии AE также попадает на «Блок регенерации 1», а именно, на нижний вход элемента L3 (логическое «И»), то есть на нижний вход элемента L3 подается логическая единица.

Рассмотрим, как в этом случае будет работать блок регенерации.

Так как от контроллера памяти нет никаких сигналов, то на входе элемента L1 (логическое «НЕ») будет логический ноль, а, соответственно, на выходе – логическая «1». Таким образом, на верхнем входе элемента L3 (логическое «И») будет логическая единица.

Имея на входах элемента L3 (логическое «И») две логические единицы, на выходе получим так же логическую единицу.

На выходе элемента L2 (логическое «И») будет логический ноль, так как на обоих его входах напряжение отсутствует, так как от контроллера памяти нет никаких команд и данных.

В результате, на входах элемента L4 (логическое «ИЛИ-НЕ») будет логический ноль и логическая единица, а, соответственно, на его выходе будет логический ноль, то есть напряжение будет отсутствовать. Так как напряжение отсутствует, то ни один конденсатор первого столбца матрицы памяти подзаряжен не будет. Хотя, даже если бы напряжение и присутствовало, все равно подзарядка была бы невозможна, так как транзисторы подзарядки (доля ячейки М11 – это VT1) были бы закрыты, ведь ни на одну строку матрицы памяти (S1-Sn) напряжение не подается.

Точно такая же ситуация будет со всеми столбцами матрицы памяти.

Таким образом, при бездействии памяти конденсаторы не подзаряжаются и хранят тот заряд (а, соответственно, и тот бит данных), который у них был с момента последней подзарядки. Однако долго это продолжаться не может, так как из-за саморазрядки конденсатор, через несколько десятков миллисекунд, разрядится, и данные будут утеряны. Поэтому необходимо постоянно проводить регенерацию памяти.

1.2. Работа динамической памяти при чтении данных и регенерации.

Будем рассматривать принцип чтения данных из динамической памяти на примере считывания данных из ячейки памяти М11:

1. Процессор запрашивает порцию данных (размер зависит от разрядности процессора, для 32-разрядного процессора минимальной единицей обмена, обычно, являются 32 бита) и выдает их адрес.

2. Контроллер шины памяти преобразует адрес в номер строки и номер столбца и выдает номер строки в дешифратор адреса строки. Дешифратор адреса строки выдает сигнал в соответствующую строку матриц памяти. Мы договорились, что в примере данные будем читать из первой ячейки памяти. Поэтому дешифратор адреса строки подаст напряжение на первую строку (S1).

3. Напряжение, поданное на строку S1, откроет транзисторы VT1 и VT3 первой ячейки памяти и соответствующие транзисторы всех остальных ячеек первой строки.

4. Дальнейшая работа памяти зависит от наличия или отсутствия заряда на конденсаторе. Рассмотрим отдельно два случая, когда на конденсаторе ячейки М11 есть заряд, и когда нет.

Так как на конденсаторе С ячейки памяти М11 есть заряд, то транзистор VT2 будет открыт, а, соответственно, ток, создаваемый входным напряжением Uп, пойдет по линии AB. В результате, на выходе Q1 первого столбца тока не будет. А это означает, что с ячейки памяти М11 считан ноль. Соответствующая информация о считанном бите с первого столбца будет записана в «Буфер данных».

Для поддержания транзистора VT2 в открытом состоянии и протекания тока по линии AB расходуется заряд конденсатора С. В результате, конденсатор очень быстро разрядится, если не провести его регенерацию.

Так как на выходе Q1 тока нет, то он не будет поступать и в «Блок регенерации 1», а, соответственно, на нижнем входе элемента L3 (логическое «И») будет логический ноль.

Так как мы рассматриваем случай чтения данных, то сигнал записи V1 и данные для записи D1 в «Блок регенерации 1» подаваться не будут. В остальные блоки регенерации соответствующие сигналы D1-Dm и V1-Vm также подаваться не будут.

В результате, на входе элемента L1 (логическое «НЕ») будет логический «0», а на выходе – логическая «1», поэтому на входах элемента L3 (логическое «И») будет логический «0» и логическая «1». Это значит, что на выходе этого элемента будет логический «0».

На выходе логического элемента L2 (логическое «И») будет логический ноль, так как на обоих его входах напряжение отсутствует, так как от контроллера шины памяти отсутствуют команды на запись и данные для записи.

Имея на обоих входах элемента L4 (логическое «ИЛИ-НЕ») логический «0», на его выходе будем иметь логическую «1», то есть с блока регенерации пойдет ток подзарядки конденсатора С. Так как транзистор подзарядки VT1 ячейки памяти М11 открыт, то ток подзарядки беспрепятственно пройдет в конденсатор С. Остальные ячейки памяти первого столбца имеют закрытый конденсатор подзарядки, а, следовательно, подзарядка их конденсаторов происходить не будет.

Ток, создаваемый входным напряжением Uп, пойдет по линии AЕ, так как транзистор VT2 будет закрыт. Следовательно, на входе Q1 «Буфера данных» будет ток, что означает – с ячейки памяти считана единица. Информация о считанном бите с первого столбца будет записана в «Буфер данных».

Так как в конденсаторе заряда не было, то и подзаряжать его надобности нет. Следовательно, с блока регенерации ток пойти не должен.

Так как на выходе Q1 ток есть, то он поступает и в «Блок регенерации». Следовательно, на нижний вход элемента L3 (логическое «И») подается логическая единица.

Так как мы рассматриваем случай чтения данных, то сигнала записи V1 и данных для записи D1 в «Блок регенерации 1» подаваться не будет. Так же в остальные блоки регенерации, соответствующие сигналы D1-Dm и V1-Vm так же подаваться не будут.

Следовательно, на входе элемента L1 (логическое «НЕ») будет логический ноль, а на выходе – логическая «1». Таким образом, на входах элемента L3 (логическое «И») будут две логические единицы. В результате, на выходе получим так же логическую единицу.

На выходе логического элемента L2 (логическое «И») будет логический ноль, так как на обоих его входах напряжение отсутствует, так как от контроллера памяти нет команд на запись и данных для записи.

В результате, на входах элемента L4 (логическое «ИЛИ-НЕ») будет логический ноль и логическая единица, а, соответственно, на его выходе будет логический ноль, то есть напряжение будет отсутствовать. Так как напряжение отсутствует, то ни один из конденсаторов первого столбца матрицы памяти подзаряжаться не будет.

5. Параллельно с чтением и регенерацией данных первого столбца происходит по такому же алгоритму чтение данных с остальных столбцов. В результате, в буфер данных будет записано значение всех ячеек памяти первой строки.

6. С контроллера памяти на дешифратор адреса столбца выдаются номера столбцов для считывания. За один такт номера считываются сразу с нескольких столбцов. Количество столбцов для считывания определяется разрядностью процессора и способом его взаимодействия с памятью. Для 32-разрядных процессоров минимальной порцией является считывание данных с 32 столбцов.

7. С дешифратора адреса столбцов номера столбцов передаются в «Буфер данных», откуда соответствующие данные считываются и передаются в процессор.

На этом цикл чтения данных заканчивается. Как вы заметили, при чтении данных считываются значения сразу со всей строки памяти данных, а потом из нее в «Буфере данных» выбираются нужные данные. Поэтому минимальной порцией чтения данных с динамической оперативной памяти является строка.

При чтении данных одновременно происходит и их регенерация. Однако не все данные ОЗУ постоянно нужны для работы, поэтому обращение к некоторым ячейкам памяти может быть очень редким. Для того чтобы данные в таких ячейках не были утеряны, их приходится считывать принудительно, не дожидаясь пока они потребуются процессору.

Поэтому «Блок управления» с определенной частотой, в моменты простоя памяти или между обращением к памяти процессора (или других устройств), регенерирует данные во всех ячейках памяти.

1.3. Работа динамической памяти при записи данных.

Будем рассматривать принцип записи данных в динамическую память на примере записи данных в ячейку памяти М11:

1. Контроллер шины памяти получает команду на запись данных, данные и адрес, куда необходимо записать эти данные.

2. Контроллер шины памяти преобразует адрес на две составляющие – номер строки и номера столбцов, и передает полученные составляющие в «Дешифратор адреса строки» и в «Дешифратор адреса столбцов». А данные передает в «Блок работы с данными».

3. Дешифратор адреса строки выдает сигнал в соответствующую строку матрицы памяти. Мы договорились, что в примере данные будем записывать в первую ячейку памяти. Поэтому дешифратор адреса строки подаст напряжение на первую строку (S1).

4. Одновременно с «Дешифратора адреса столбцов» выдаются сигналы V в столбцы, соответствующие полученному адресу. В эти же столбцы подаются сигналы D с «Блока работы с данными», уровень которых определяется значением битов записываемого слова.

5. Напряжение, поданное на строку S1, откроет конденсаторы VT1 и VT3 первой ячейки памяти и соответствующие конденсаторы всех остальных ячеек первой строки.

6. Если в ячейке М11 хранится бит со значением «0» (в конденсаторе есть заряд), то ток, создаваемый входным напряжением Uп, пойдет по линии AB, иначе – по линии AE. Но нам это не важно, так как в ячейку М11 производится запись данных, а не их чтение, поэтому буфер данных будет игнорировать считанное с ячейки значение. А с выхода элемента L3 «Блока регенерации 1» будет всегда идти логический ноль, так как с дешифратора столбцов приходит сигнал (V1) на запись данных в первый столбец.

В результате, на входе элемента L1 будет логическая единица, а на выходе – логический ноль. Соответственно, на верхнем входе элемента L3 мы всегда имеем логический ноль, что означает – независимо от значений на нижнем входе, на выходе элемента L3 будет логический ноль.

На нижнем входе элемента L2 будет логическая единица, так как с дешифратора адреса столбцов выдается сигнал V1, а на верхнем входе будет либо ноль, либо единица, в зависимости от того, какое значение имеет бит записываемой информации.

Если бит имеет значение «1», то на верхнем входе элемента L2 будет «1». Имея две единицы на входе, мы получим на выходе так же логическую единицу. Соответственно, на входах элемента L4 будет получена логическая «1» и логический «0». В результате, на выходе будет логический «0», то есть ток будет отсутствовать, а, соответственно, зарядка конденсатора C идти не будет. Если до этого конденсатор С содержал заряд, то через несколько микросекунд он разрядится, пропуская ток по линии АВ. Таким образом в конденсатор С будет записан бит данных «1», соответствующий разряженному состоянию конденсатора.

Если бит имеет значение «0», то на верхнем входе элемента L2 будет «0». Имея на верхнем входе логический ноль, а на нижнем – логическую единицу, на выходе элемента L2 получим логический ноль. В результате, на верхнем и нижнем входах элемента L4 имеем логические нули, что означает – на выходе элемента L4 будет логическая единица, то есть пойдет ток зарядки конденсатора. Таким образом в конденсатор С будет записан бит данных «0», соответствующий заряженному состоянию конденсатора.

Аналогичным образом будут записаны данные в другие столбцы матрицы памяти. В тех столбцах, в которых запись данных не требуется, будет произведено чтение данных из ячейки памяти и ее регенерация. При этом данные в буфер памяти записаны не будут.

Запись данных во все требуемые ячейки строки матрицы памяти и чтение с регенерацией из оставшихся ячеек строки производятся параллельно.

Приведенная на рисунке 1 структурная схема памяти и описанный принцип работы соответствуют одной из самых простых организаций динамической памяти. На практике такую память уже давно не используют. Со временем, она претерпела ряд изменений, позволивших ей работать гораздо быстрее. Давайте рассмотрим эти улучшения.

2. Этапы модернизации динамической оперативной памяти.

Все усовершенствования в работе динамической памяти были направлены на увеличение скорости работы памяти, так как скорость оперативной памяти всю историю существования вычислительной техники являлась одним из факторов, сдерживающих рост производительности ЭВМ. Если обратиться к истории ЭВМ, то можно увидеть, что каждый прорыв в области организации оперативной памяти приводил к резкому скачку в быстродействии ЭВМ.

Естественно, скорость работы памяти увеличивалась, за счет повышения тактовой частоты и улучшения технологического процесса производства. Это был закономерный процесс, приводивший к плавному увеличению скорости работы. Но нас более интересуют изменения в принципиальном устройстве памяти, приводившие к появлению новых типов памяти. Именно о них я буду рассказывать в этой главе.

2.1. PM DRAM.

Один из первых видов оперативной памяти, используемой в персональных компьютерах, была простая динамическая оперативная память (PM DRAM – Page Mode DRAM), принцип работы которой описан выше. PM DRAM использовалась вплоть до середины 90-х годов.

Однако ее быстродействия катастрофически не хватало, поэтому на смену ей в 1995 году пришла память FPM DRAM.

2.2. FPM DRAM.

FPM DRAM (Fast Page Mode DRAM) – быстрая страничная память. Основное ее отличие от памяти FP DRAM заключалось в поддержке сохраненных адресов. То есть, если новое считываемое из памяти слово находилось в той же строке, что и предыдущее слово, то обращение к матрице памяти не требовалось, а выборка данных осуществлялась из «Буфера данных» (смотри рисунок 1) по номерам столбцов. Это позволяло в случае чтения из памяти массивов данных значительно сократить время чтения.

Однако запись данных в память осуществлялась точно так же, как и в памяти PM DRAM. Да и далеко не всегда считываемые данные располагались в одной строке. В результате, прирост производительности сильно зависел от типа программ, с которыми работала ЭВМ. Прирост мог быть, как существенный, так и вовсе могло быть замедление работы, из-за дополнительных накладных расходов на анализ номера строки предыдущей операции чтения.

Следующий тип памяти, заменивший FPM DRAM, появился через год (в 1996 году) и назывался EDO-DRAM.

2.3. EDO-DRAM.

EDO-DRAM (Extended Data Out DRAM) – динамическая память с усовершенствованным выходом. В этом типе памяти адрес следующего считываемого слова передавался до завершения считывания линии данных памяти, то есть до того, как считанные данные из памяти были переданы процессору.

Приступить к считыванию нового слова данных, до завершения чтения предыдущего, стало возможным, благодаря вводу, так называемых, регистров – защелок, которые сохраняли последнее считанное слово даже после того, как начиналось чтение или запись следующего слова.

Сочетая в себе также новшества памяти FPM RAM, новый тип памяти давал прирост производительности в пике, достигавший 15-20%.

Однако прогресс не стоял на месте, тактовые частоты работы процессоров, системной шины и естественно памяти росли. С повышением тактовой частоты все сложнее было добиваться стабильной работы памяти EDO-DRAM, так как из-за непредвиденных задержек чтение нового слова данных могло начаться прежде, чем предыдущее слово данных было сохранено с помощью регистров-защелок.

В результате, на смену EDO-DRAM пришла память SDRAM.

2.4. SDRAM.

SDRAM (Synchronous DRAM) – синхронная динамическая память с произвольным доступом. Как видно из названия, память работала синхронно, синхронно с контроллером памяти, что гарантировало завершение цикла чтения/записи строк в заданное время. Это позволяло выдавать новую команду на чтение до завершения считывания предыдущего слова данных, будучи уверенным, что считывание завершится верно, а чтение нового слова начнется с минимальной задержкой.

Однако тут возникали проблемы с чередованием чтения и записи. Когда подряд считывалось несколько слов данных – проблем не было никаких, а вот если до окончания записи приходила команда на чтение слова, которое записывалось, то это могло привести к считыванию неверных данных. Поэтому контроллер синхронной памяти дополнительно усложнился, обеспечивая защиту от таких ситуаций.

Также в SDRAM памяти было увеличено количество матриц памяти с одной до двух, иногда до четырех. Это позволило во время обращения к одной матрице памяти регенерировать строки другой матрицы, что, в свою очередь, позволило поднять тактовую частоту работы памяти, из-за уменьшения задержек на регенерацию.

Также это позволило считывать данные сразу из нескольких матриц памяти. То есть, пока идет считывание из одной матрицы памяти, в другую уже передается адрес нового слова для чтения/записи.

Со временем, развитие технологии производства и возможность работы сразу с несколькими матрицами памяти позволили значительно поднять внутреннюю скорость работы микросхем оперативной динамической памяти. Внешняя шина памяти стала узким местом и замедляла работу. В результате, был разработан новый тип памяти DDR SDRAM. С появлением DDR SDRAM предшествующую память SDRAM стали называть SDR SDRAM (Single Data Rate DRAM).

2.5. DDR SDRAM.

DDR SDRAM (Double Data Rate SDRAM) – синхронная динамическая память с произвольным доступом и удвоенной частотой передачи данных.

В этом типе оперативной памяти обмен данными по внешней шине идет не только по фронту тактового импульса, но и по спаду. В результате, без увеличения тактовой частоты внешней шины удваивается объем передаваемой информации.

Но подъема скорости работы внешней шины данных недостаточно, необходимо, чтобы и сама память поддерживала такую скорость. Так как увеличить частоту работы оперативной памяти довольно сложно, трудоемко и дорого, то производители пошли на хитрость. Вместо увеличения тактовой частоты памяти, они увеличили разрядность внутренней шины данных (от ячеек матриц памяти до буферов ввода-вывода) и сделали ее в два раза большей, чем разрядность внешней шины памяти (от контроллера памяти, встраиваемого в северный мост, или процессора до микросхемы памяти). То есть за 1 такт считывалось столько данных, сколько могло передаваться по внешней шине только за два такта. При этом ширина внешней шины данных составляла 64 бита, а внутренней – 128 бит.

В результате, по фронту тактового импульса из чипа памяти передавалась первая часть данных, а по спаду – вторая. Аналогичная ситуация была и при записи данных в память. Сначала принималась первая часть данных, а затем – вторая, после чего они обрабатывались одновременно.

Однако из-за накладных расходов и необходимости применять мультиплексор, для объединения двух частей данных, передаваемых в оперативную память, и демультиплексор, для разделения считываемых данных из памяти на две части, сильно выросла латентность памяти.

Латентность – это время между запросом данных из памяти и временем, когда оперативная память начнет выдавать требуемые данные.

В результате, реальная производительность DDR памяти, по сравнению с SDR, возросла всего лишь на 30-40 процентов.

Наиболее популярные модели памяти DDR работали на тактовой частоте 200 МГц, но имели маркировку DDR400. 400 означало количество транзакций (обменов) в секунду. Действительно, при тактовой частоте 200 МГц и передаче данных по фронту и спаду тактового импульса, в секунду будет совершаться 400 МТр. При этом внутренняя частота чипа памяти также будет 200 МГЦ.

С появлением DDR памяти, одним из актуальных параметров работы чипа памяти стала латентность. В результате, для примерной оценки производительности памяти ввели такое понятие, как тайминги памяти.

Тайминги, обычно, задаются набором из четырех чисел, определяющих основные задержки памяти в тактах работы чипа памяти. В таблице 1 приведен пример расшифровки таймингов памяти DDR266 (тайминги: 2.5-3-3-7) в порядке их расположения в строке.

| Тайминги | Значение | Расшифровка |

| Tcl | 2.5 | CAS Latency – задержка в тактах между выдачей в память адреса столбца, когда нужная строка уже открыта, и началом выдачи данных из памяти. |

| Trcd | 3 | Row to CAS Delay – задержка в тактах между открытием строки и разрешением доступа к столбцам или, другими словами, задержка между подачей номера строки и номера столбца. |

| Trp | 3 | Row Precharge Time – время в тактах, требуемое на закрытие одной строки и открытие другой, или, другими словами, задержка между чтением последней ячейки памяти и подачей номера новой строки. |

| Tras | 7 | Tras (Active to Precharge Delay) – минимальное время между подачей номера строки и подачей команды подзарядки ячеек строки (PRECHARGE), то есть количество тактов, затрачиваемое памятью на чтение данных. |

Таблица 1. Расшифровка таймингов оперативной памяти.

С помощью таймингов можно определить:

Тайминги можно изменять (разгонять память), наряду с тактовой частотой, однако стабильность работы памяти при этом не гарантируется, поэтому надо быть крайне внимательными и осторожными при попытках заставить работать память с нестандартными настройками.

В таблице 2 приведены основные сертифицированные стандарты DDR SDRAM и их параметры.

| Стандарт | Частота внутренней шины, МГц | Частота внешней шины, МГц | Количество транзакций в секунду, МТр | Стандартные тайминги* | Теоретическая пропускная способность, Мб/с |

| DDR200 | 100 | 100 | 200 | 2-2-2-5 | 1600 |

| DDR266 | 133 | 133 | 266 | 2.5-3-3-7 | 2133 |

| DDR300 | 166 | 166 | 333 | 2.5-3-3-7 | 2667 |

| DDR400 | 200 | 200 | 400 | 2.5-3-3-8 | 3200 |

* У различных производителей стандартные тайминги могут варьироваться и сильно зависят от качества элементной базы.

Таблица 2. Параметры стандартов памяти DDR SDRAM.

Поднять тактовую частоту чипа памяти выше 200 МГц на том этапе было крайне затруднительно. Естественно существовала память, работающая на тактовой частоте 233, 250 и даже 267 МГц, но это были несертифицированные стандарты, и стоили они дорого.

В результате, разработчики памяти продолжили развивать архитектуру памяти DDR SDRAM. Логическим результатом этого развития стала память DDR2 SDRAM.

2.6. DDR2 SDRAM.

В памяти DDR2 SDRAM ширина внутренней шины данных была увеличена еще в два раза и стала превосходить внешнюю шину данных в четыре раза. В результате, при одной и той же тактовой частоте внешней шины памяти у памяти DDR2 SDRAM внутренняя тактовая частота была в два раза меньше, по сравнению с памятью DDR SDRAM.

Для сравнения возьмем топовую память DDR (DDR400) и первую спецификацию памяти DDR2 (DDR2-400). Казалось бы, раз это новый тип памяти, то он должен работать быстрее, однако дело тут обстояло совсем не так. На практике память DDR2-400 была чуть ли не медленнее памяти DDR400.

Давайте разберемся почему. И так, первое – это тактовая частота внешней шины данных. Она была у обоих типов памяти одинаковая – 200 МГц, и ширина внешней шины данных тоже была одинаковая – 64 разряда. В результате, и быстродействие у памяти DDR2-400 заметно выше, чем у памяти DDR400, быть не могло.

К тому же в памяти DDR400 ширина внутренней шины была всего в 2 раза больше внешней, тогда как у DDR2-400 – в четыре. В результате, устройство мультиплексора и демультиплексора памяти DDR2-400 – сложнее. К тому же далеко не всегда считываемые/записываемые данные находятся в одной строке матрицы памяти, в результате, считать/записать все слова данных одновременно невозможно, эта особенность тем негативнее сказывается, чем больше ширина внутренней шины данных, а она, естественно, больше у памяти DDR2.

Так в чем же преимущество памяти DDR2-400. А преимущество – в тактовой частоте чипа памяти. Она была в два раза ниже, чем тактовая частота чипа DDR-400. Это давало огромный потенциал для увеличения производительности памяти и уменьшало энергопотребление.

В результате, очень быстро появилась память с внешней шиной, работающей на тактовой частоте 400 МГц. А позже у топовых моделей памяти DDR2 тактовая частота внешней шины достигла 533 МГц, при тактовой частоте чипа памяти – 266 МГц, и пиковой теоретической пропускной способности – 9.6 Гб/с, что, несмотря на увеличившуюся латентность, значительно превосходило возможности памяти DDR.

В таблице 3 приведены основные стандарты DDR2 SDRAM и их параметры.

| Стандарт | Частота внутренней шины, МГц | Частота внешней шины, МГц | Количество транзакций в секунду, МТр | Стандартные тайминги* | Теоретическая пропускная способность, Мб/с |

| DDR2-400 | 100 | 200 | 400 | 3-3-3-12 | 3200 |

| DDR2-533 | 133 | 266 | 533 | 5-5-5-15 | 5300 |

| DDR2-667 | 166 | 333 | 667 | 2.5-3-3-7 | 2667 |

| DDR2-800 | 200 | 400 | 800 | 5-5-5-15 | 7100 |

| DDR2-1066 | 266 | 533 | 1066 | 5-5-5-15 | 8500 |

| DDR2-1200 | 300 | 600 | 1200 | 5-5-5-15 | 9600 |

* У различных производителей стандартные тайминги могут варьироваться и сильно зависят от качества элементной базы.

Таблица 3. Параметры стандартов памяти DDR2 SDRAM.

На этом был практически достигнут предел возможности усовершенствования DDR2 памяти по частоте и латентности. Дальнейшее увеличение производительности приводило к значительному росту энергопотребления и тепловыделений, и снижения стабильности и надежности работы памяти.

В результате, разработчики в 2005 году представили прототипы нового поколения DDR SDRAM памяти – DDR3 SDRAM. Однако массовое производство этой памяти и экспансия рынка начались только в 2009 году.

2.7. DDR3 SDRAM.

Основное направление развития памяти DDR3 SDRAM сохранилось таким же, как у DDR2 SDRAM. То есть снова была увеличена вдвое ширина внутренней шины данных памяти, что привело к снижению внутренней тактовой частоты памяти в два раза. К тому же при производстве памяти применялся новый технологический процесс, в начале – до 90 нм, затем – до 65 нм, 50 нм, 40 нм, и видимо это еще не предел.

Все это открыло разработчикам дальнейшие возможности по наращиванию тактовой частоты внешней шины памяти, тактовой чистоты самого чипа памяти, снижению рабочего напряжения и увеличению объема памяти.

Однако вместе с увеличением ширины внутренней шины данных увеличилась латентность памяти, усложнилось устройство мультиплексора/демультиплексора. В общем, все проблемы DDR и DDR2 памяти перешли в DDR3 память.

Но, благодаря улучшению технологического процесса и архитектуры памяти, удалось снизить время цикла чтения/записи, что позволило несколько снизить влияние увеличившейся латентности на производительность памяти.

В таблице 3 приведены существующие стандарты DDR3 SDRAM и их основные параметры.

| Стандарт | Частота внутренней шины, МГц | Частота внешней шины, МГц | Количество транзакций в секунду, МТр | Стандартные тайминги* | Теоретическая пропускная способность, Мб/с |

| DDR3-800 | 100 | 400 | 800 | 6-6-6-18 | 6400 |

| DDR3-1066 | 133 | 533 | 1066 | 7-7-7-21 | 8533 |

| DDR3-1333 | 166 | 667 | 1333 | 8-8-8-24 | 10667 |

| DDR3-1600 | 200 | 800 | 1600 | 8-8-8-24 | 12800 |

| DDR3-1866 | 233 | 933 | 1866 | 9-9-9-27 | 14930 |

| DDR3-2000 | 250 | 1000 | 2000 | 9-9-9-27 | 16000 |

| DDR3-2133 | 266 | 1066 | 2133 | 9-11-9-28 | 17066 |

| DDR3-2200 | 275 | 1100 | 2200 | 10-10-10-30 | 17600 |

| DDR3-2400 | 300 | 1200 | 2400 | 9-11-9-28 | 19200 |

* У различных производителей стандартные тайминги могут варьироваться и сильно зависят от технологического процесса производства и качества элементной базы.

Таблица 4. Параметры стандартов DDR3 SDRAM.

Память DDR3 сегодня (начало 2012 года) занимает главенствующие позиции на рынке, однако ей уже грядет замена в лице нового поколения памяти DDR – DDR4 SDRAM.

2.8. DDR4 SDRAM.

Стандарты нового поколения памяти были представлены еще в 2008 году в Сан-Франциско на форуме, организованном компанией Intel. В 2011 году компания Sumsung продемонстрировала свои первые прототипы памяти DDR4.Однако начало производства этого типа памяти планируется на 2012 год, а окончательное завоевание рынка закончится не ранее 2015 года. Такие поздние сроки начала массового производства, в основном, связаны с тем, что возможности памяти DDR3 еще полностью не исчерпаны и позволяют удовлетворить требования большинства пользователей. А, следовательно, выход на рынок с новым типом памяти будет коммерчески неоправдан.

Память DDR4 продолжит тенденции DDR памяти. Будет увеличена ширина внутренней шины, улучшена технология производства до 32-36 нм, подняты тактовые частоты внешней и внутренней шины, а также будет снижено напряжение.

Но поговорим о ней более подробно, когда появятся первые массово выпускаемые образцы памяти, а сейчас подведем итоги обзора динамической памяти и сформулируем ее основные достоинства и недостатки.

3. Достоинства и недостатки динамической памяти.

Преимущества динамической памяти:

Недостатки динамической памяти: