Что такое IMC (контроллер памяти) процессора

IMC на самом деле является одной из тех частей процессора, которые обычно не принимаются во внимание, и это то, что мы склонны смотреть только на ядра, скорость и, самое большее, на кеш-память, которую они имеют. Но это внутренний компонент процессоров, который чрезвычайно важен, и тогда вы поймете, почему.

Что такое ИМТ процессора

Как работает контроллер памяти?

Контроллеры памяти содержат логику, необходимую для чтения и записи в ОЗУ и «обновления» DRAM. Без этих постоянных «обновлений» DRAM потерял бы содержащиеся в нем данные, так как содержащиеся в них конденсаторы теряют заряд за доли секунды (не более 64 миллисекунды в соответствии со спецификацией JEDEC ).

Чтение и запись в ОЗУ осуществляется путем выбора адресов данных строки и столбца DRAM в качестве входов для схемы мультиплексора, где демультиплексор в DRAM использует преобразованные входы для выбора правильного расположения в памяти и возврата данных, которые возвращаются обратно через мультиплексор для консолидации с целью уменьшения ширины шины, необходимой для работы.

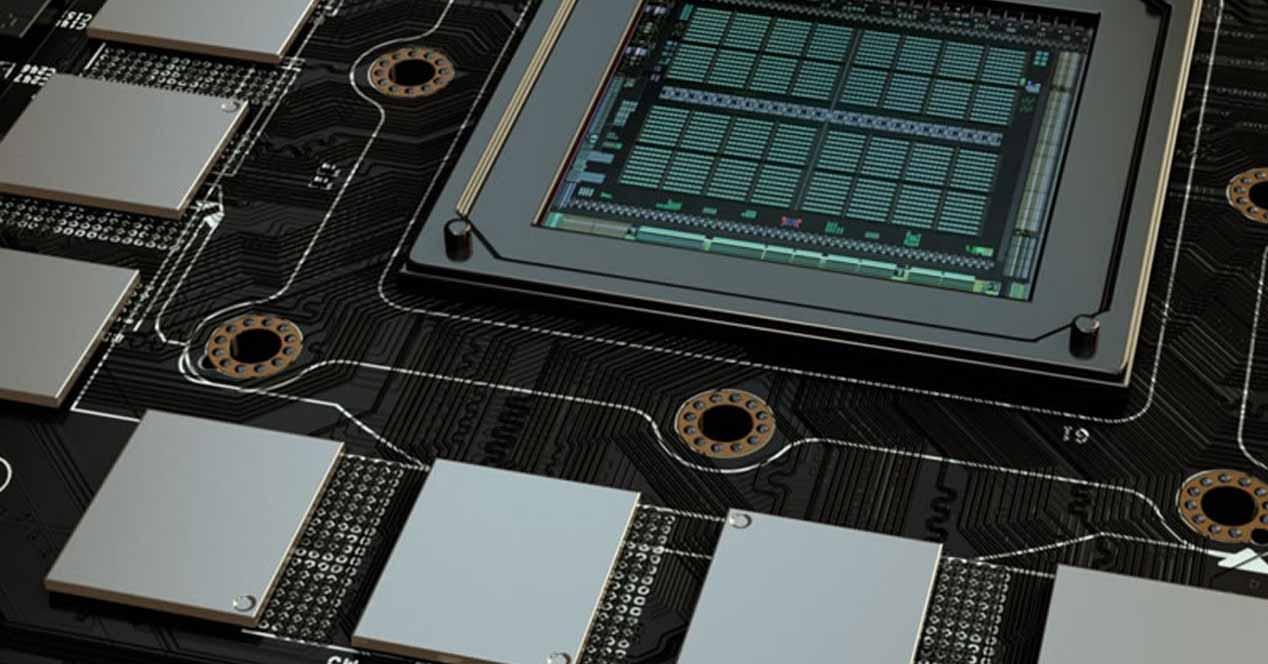

ширина шины памяти представляет количество параллельных линий, доступных для связи с ячейкой памяти. Ширина шины контроллеров памяти варьируется от 8 бит в старых системах до 512 бит в более современных видеокартах и системах (как правило, реализуются в виде четырех одновременных 64-битных контроллеров памяти, которые работают параллельно, хотя некоторые предназначены для работы в «групповом режиме» где два 64-битных контроллера памяти могут использоваться для доступа к 128-битному устройству памяти).

Некоторые контроллеры памяти также имеют свою собственную систему исправления ошибок, которая может быть дополнена той, которая включает в себя множество модулей памяти ОЗУ (что хорошо, потому что в некоторых случаях она освобождает их, а в других удваивает коррекцию ошибок размера).

Варианты существующего ИМТ

Конечно, вы заметили, что спецификации процессоров почти всегда включают определение типа и скорости ОЗУ, с которым они совместимы, точно в зависимости от ИМТ, который они включают. Поэтому существуют разные варианты контроллера памяти, и некоторые из них вы обязательно узнаете сразу.

С другой стороны, у нас есть контроллеры с именем FBM ( Полностью буферизованная память ) поведение которого отличается от предыдущего тем, что в каждом модуле памяти находится буферное устройство (называемое FB-DIMM ), который использует последовательный канал передачи данных к контроллеру (вместо параллельного), уменьшая количество рельсов, необходимых для связи, за счет увеличения задержки.

Наконец, мы имеем Флэш-память контроллеры, используемые такими устройствами, как флеш-накопители или твердотельные накопители. Флэш-память по своей природе медленнее, чем DRAM, и, как правило, становится непригодной для использования после ряда циклов записи, но ей все равно нужен собственный контроллер памяти для связи с остальной системой.

Особенности контроллера памяти в процессорах для LGA1366

C момента появления процессоров на ядре Nehalem, одним из их преимуществ все считали интегрированный трехканальный контроллер памяти. Не просто интегрированный контроллер памяти (ИКП сокращенно), а именно трехканальный. Понятно, чем это «круто» — все-таки одноканальные и двухканальные контроллеры памяти у AMD были еще за пять лет до этого, так что дополнительный канал, да еще и наиболее скоростной на данный момент памяти типа DDR3, выглядел весьма серьезным преимуществом. По мнению многих пользователей, также и одним основных факторов, которым процессоры линейки Core i7 обязаны своей высокой производительностью. Стоит заметить, что сама компания Intel это мнение никак не опровергала, за что и немного поплатилась — по-настоящему массовые процессоры архитектуры Nehalem, которые будут выпущены в начале осени, рассчитаны на конструктив LGA1156, предполагающий использование лишь двух каналов памяти. Казалось бы, серьезный недостаток новых моделей, который неспособен будет позволить им конкурировать со старшими братьями. Но так ли это?

Конфигурация тестовых стендов

Все тестирование проводилось с использованием процессора Core i7 920, материнской платы Intel DX58SO («Smackover») и референс-видеокарты на базе NVIDIA GeForce GTX 275 — словом, как все положено, согласно версии 4.0 нашей методики тестирования. Различалась только память. В дополнение к обычно используемому нами комплекту Kingston KVR1333D3N9K3/6G, мы взяли еще и кит от Apacer, имеющий вдвое меньший объем. Все модули поддерживают работу на более высоких частотах, нежели официальные для Core i7 920 1066 МГц, но мы тестировали их именно на этой частоте по схеме 8-8-8-19.

Получилось четырех конфигурации, представленные в таблице:

| Число каналов | Общий объем | |

| 3×2 | 3 | 6 ГБ |

| 2×2 | 2 | 4 ГБ |

| 1×4 | 1 | 4 ГБ |

| 3×1 | 3 | 3 ГБ |

Почему именно они? Две трехканальных нам нужны, чтобы четко понять — что важно в каком-то приложении: трехканальность или суммарный объем? Это будет хорошо видно по результатам: если и 3×2, и 3×1 в победителях, значит, польза от трех каналов есть, если только первый, значит, приложению просто нужно много памяти (точнее, оно способно ее использовать). Без 3×1 к однозначному ответу прийти было бы сложно. Полезность участия в тестах 2×2 очевидна — именно таким образом комплектуются современные системы на Core 2 и процессорах AMD, и именно он на некоторое время станет весьма массовым для систем на LGA1156 (конечно, можно было бы протестировать память и в конфигурации 2×1, но это уже с точки зрения систем, не относящихся к бюджетному сектору, совсем не интересно). 1×4 выглядит крайне синтетичным, поскольку вряд ли кто-то, имея два модуля памяти по 2 ГБ, будет их устанавливать в один канал, «презрев» остальные, однако… Он нам нужен для повышения общей образованности. Да и модули DDR3, емкостью 4 ГБ, уже появились. К сожалению, пока это экзотика, даже до наших рук не добравшаяся (иначе бы в списке тестируемых обязательно был бы и вариант 2×4), однако массовое распространение на рынке, как таких модулей, так и китов на их основе лишь вопрос времени.

Подробные результаты всех подтестов, как обычно, представлены в таблице, в формате Excel. Заметим, что в сегодняшнем тестировании они будут иногда даже более интересными, чем общие усредненные показатели по группам, так что тем, кому интересна детальная информация, не стоит отказывать себе в удовольствии с ними познакомиться.

Пристрелка

Но для начала мы решили проверить производительность каждого из вариантов в синтетическом приложении, в роли которого сегодня выступал Everest 4.6 (да, это далеко не последняя версия популярного тестового пакета, однако и «реальный» софт обновляется далеко не мгновенно, так что эти результаты нам весьма интересны даже если предположить слабую оптимизированность 4.6 под Nehalem).

И первые же результаты несколько обескураживают — как мы видим, никакого видимого прироста от задействования третьего канала ИКП нет. Более того — три модуля от Apacer справляются с этой задачей медленнее, чем два от Kingston. В то же время одноканальный режим — явный аутсайдер. Теоретическая ПСП DDR3 1066 составляет 8528 МБ/с, во что мы и уперлись — это понятно. Но добавление еще одного канала увеличивает скорость чтения далеко не в два, а менее чем в полтора раза, а третий вообще ничего не дает.

Со скоростью записи все еще веселее — одноканальный режим честно уперся в теоретическую ПСП, а увеличение количества каналов дало лишь менее 20% во всех случаях.

И, наконец, задержки доступа. Очевидный лидер здесь — двухканальный режим (напомним, что на этой диаграмме чем меньше цифры, тем лучше), хотя и одноканальный доступ дело не сильно ухудшает, но в трехканальном режиме задержки сравнительно сильно возрастают: на четверть.

Уже можно делать определенные выводы. Как мы помним из поведения других архитектур с ИКП (AMD K8/K10), они наиболее восприимчивы именно к задержкам при доступе к памяти, что очень заметно в реальных приложениях. Вряд ли Nehalem будет вести себя строго наоборот. Причем все это на фоне одинаковых скоростей чтения и записи, то есть двухканальный режим должен стать лидером. Одноканальный — уже не факт, что будет слишком быстрым: задержки меньше, но и ПСП гораздо ниже, а это не может не сказаться. Насколько сильно — мы и проверим. И попутно посмотрим, как разные приложения относятся к разному полному объему памяти: синтетические бенчмарки никакой информации по этому поводу дать не могут.

3D-визуализация

В аутсайдерах оказались обе трехканальных конфигурации, из чего можно сделать вывод, что главное для этой группы приложений — задержки доступа. Но эти два варианта ведут себя по-разному, а изучение подробных результатов тестов показывает достаточно пеструю картину, из чего можно сделать вывод, что некоторым приложениям уже недостаточно не только трех, но и четырех гигабайт памяти.

Рендеринг трёхмерных сцен

Рендеринг вообще мало восприимчив к характеристикам системы памяти, что можно было предполагать и изначально — здесь главное именно «числодробительные» способности вычислительных ядер и их количество (да и «виртуальные» потоки вычисления тоже воспринимаются положительно). Причем и к объему памяти требований особых нет — лишь бы ее хватало для просчитываемой сцены и накладных расходов. Для наших тестов вполне достаточно 3 ГБ, что и демонстрирует нам диаграмма выше.

Научные и инженерные расчёты

А в этой группе появляется еще один класс приложений, в дополнение к тем, кому нужно как можно больше памяти и кому объем не важен — те, кто начинает в зависимости от увеличения ОЗУ работать медленнее. На первый взгляд, ситуация необъяснимая — если скорость падает от нехватки памяти, это понять легко, но избыток просто никто не должен «заметить». С другой стороны — а почему не должен? Эффективность кэширования вполне может зависеть от объема ОЗУ и даже должна от него зависеть. Если конкретное приложение использует лишь небольшой объем памяти, причем постоянный, ему будет «доставаться» разный объем кэш-памяти процессора. Например, при шести установленных гигабайтах лишь половина из 8 МБ кэша L3 будет отведена для данных программы «переднего плана» (не забываем, что в оставшейся памяти тоже может кто-то «жить», пусть и не очень активно, но на кэш при этом претендовать), а при трех их обслуживанием будут заниматься уже 2/3 от 8 МБ. Любопытный эффект, конечно, жаль только несколько в стороне от основной темы нашего исследования лежащий. С ней все, как обычно — в среднем, самым быстрым оказывается двухканальный режим, а из двух вариантов трехканального, несмотря на наличие упомянутых выше приложений-ренегатов, производительнее тот, где суммарный объем памяти выше.

Растровая графика

| Core 2 Quad Q9300 2×2 | Core i7 920 3×2 | Core i7 920 2×2 | Core i7 920 1×4 | Core i7 920 3×1 |

| 0:09:07 | 0:04:45 | 0:08:05 | 0:08:12 | 0:17:42 |

Вывод? Несмотря на то, что большинство обзоров в сети, где сравниваются процессоры разных архитектур в этом приложении (в меньшинстве обзоров теста по Photoshop просто нет, так что можно даже сказать, что во всех статьях такого рода), утверждается, что Core i7 просто идеальный процессор для Photoshop, как мы видим, ничего особо выдающегося в нем нет. Идеальным тут является не архитектура ядра, а количество памяти. При 6 ГБ Core i7 920 вдвое обгоняет Core 2 Quad Q9300, обеспеченный всего 4 ГБ. Именно такие сравнения в большинстве статей и встречаются (в том числе и на нашем сайте, но и прочие ресурсы ведут себя аналогично): 3х2 для процессоров под LGA1366 и 2х2 для Core2, AMD Phenom и т.п. Но если мы ограничим первый из процессоров теми же 4 ГБ (причем неважно, каким образом набранными), то выясняется… что отличие от Core 2 Quad вполне укладывается в допустимое, с точки зрения разницы в тактовой частоте. А если мы «отберем» у Core i7 еще всего один гигабайт памяти (казалось бы — 3 или 4: невелика разница), то результат ухудшится еще вдвое! Это наиболее показательный пример, однако и другие подтесты ведут себя сходным образом, хоть микроскопическую, но разницу находят всегда. И ничего не поделаешь — Photoshop действительно память «любит», причем чем больше «весят» обрабатываемые в нем файлы, тем больше «любит», а все утилиты тестирования производительности в данном приложении (а не только наши самописные тесты), естественно, оперируют именно большими файлами.

Впрочем, нельзя сказать, что в высоких результатах совсем нет заслуги самого Core i7, а только преференции от большого количества памяти. Трехканальный ИКП как раз и позволяет установить больше памяти при прочих равных условиях. Но об этом подробно мы поговорим чуть позже.

Сжатие данных

Программы-архиваторы не умеют использовать слишком большой объем памяти, поэтому им он просто вредит — к доступной емкости кэш-памяти они очень восприимчивы. К задержкам основного ОЗУ еще более восприимчивы, поэтому и имеем такую картину — самой медленной конфигурацией является 3х2, а выйти на первое место 3х1 мешает латентность.

Компиляция (VC++)

Компилируемый нами проект большого количества памяти не требует, так что важны задержки, а также немного скорости чтения и записи. Поэтому двухканальный режим доступа к памяти здесь оказался лучшим, но одноканальный лишь чуть-чуть выиграл у трехканальных — латентность ниже, но и прочие параметры тоже.

Тест Java-машины оказался очень восприимчив к скорости чтения из памяти, но и ее общий объем ему достаточно важен. Именно такую картину можно было бы ожидать везде, если бы верны были наивные предположения о том, что трехканальный доступ к памяти является залогом высокой производительности, но памяти при этом много не бывает. Жаль только, что среди протестированных приложений эти мечты подтверждены буквально пару-тройку раз. Но, как раз, пример, когда подтверждены.

Кодирование аудио

Прекрасная задача — требования к системе памяти, можно сказать, отсутствуют. При рендеринге они тоже почти отсутствовали, а здесь — совсем отсутствуют. Идеальный бенчмарк процессоров, правда, отвратительный для тестирования системы в целом.

Кодирование видео

А вот тут все почти так, как должно быть в «наивной теории». Портит картинку только недостаточно заметный проигрыш двухканального режима. Точнее, будет сказать, почти незаметный. Да и тому, что он вообще есть, мы обязаны ровно одному приложению — DivX. Пример хорошей оптимизации под все особенности сегодняшние Core i7. Как он поведет себя на «завтрашних» будем проверять уже менее чем через месяц.

Игровое 3D

Очень, очень спокойная немного непонятная общая картина. Однако под внешним спокойствием в детальных результатах таится настоящая буря. Пристрастия игр сильно разделились, а у каких как — оставим в качестве задачи для самостоятельного изучения. Главный вывод — для игр (именно как множества, а не для одной конкретной игры) вопрос конфигурации памяти не является каким-то важным. В общем-то, решать его даже менее необходимо, чем вопрос выбора центрального процессора (разумеется, если речь не идет о совсем уж бюджетном секторе, типа Core 2 Duo или вообще Pentium/Celeron). Главным же вопросом, стоящим перед «хардкорным» геймером сегодня, будет: «Потяну на multi-GPU или придется свои желания как-то ограничивать?»

А зачем вообще нужен трехканальный ИКП?

Как мы видим, большой пользы от задействования третьего канала контроллера памяти в Core i7 LGA1366 нет. Канал — есть, использовать — можно, но результаты далеко не всегда улучшаются. Чаще даже, наоборот, ухудшаются. Так зачем компания Intel делала ИКП именно трехканальным? Из желания поиграть мускулами (у конкурента два, а мы все три сделаем)? Возможно, такой соблазн тоже был, но вряд ли — все-таки три канала даются достаточно высокой ценой. Причем в прямо смысле: разводка плат становится очень сложной, а сложно — значит дорого. Процессоры можно делать и недорогими (и использованный нами сегодня Core i7 920 тому яркий пример — его розничная цена как Core 2 Quad Q9650), но сама платформа оказывается дороговатой. Причем без особой пользы — для большинства «типично пользовательских» приложений сейчас легко можно ограничиться двумя модулями по 2 ГБ и не волноваться (особенно если учесть процент до сих пор использующих 32-х разрядные операционные системы, где больший объем ОЗУ просто не будет использоваться). Как было сказано в хорошем анекдоте про верблюжонка и его маму: «А зачем нам эти навороты, если мы все равно живем в зоопарке?»

В том-то и дело, что нынешние Core i7, по сути, в зоопарке и живут. Наилучшим образом под него будут приспособлены «настоящие» настольные модели, рассчитанные под исполнение LGA1156, главным (да и вообще — единственным) отличием которого от LGA1366 является поддержка «всего-навсего» двухканального режима памяти. А LGA1366 — платформа изначально серверная. В серверах нужно много памяти. Ни 4, ни 8 и даже ни 12 ГБ, а действительно много. Там и полсотни гигабайт легко могут оказаться востребованными, а то и недостаточными. Как же можно установить больше памяти в одну систему? Общий объем равен произведению количества модулей на их объем. Стало быть, нужно увеличивать либо количество, либо емкость каждого модуля. Второе — сложно и от производителей процессоров/чипсетов, вообще говоря, не зависит. Более того — освоение индустрией более «плотных» микросхем памяти благотворно сказывается на всех производителях серверных платформ одновременно, так что не может стать конкурентным преимуществом.

Значит, надо увеличивать количество поддерживаемых модулей. А оно равно (в общем случае) количеству контроллеров памяти, умноженных на количество поддерживаемых каждым модулей. Последнее — произведение числа поддерживаемых каналов на число одновременно работающих на каждом канале модулей. Увеличивать последнее — очень сложная задача, поскольку одновременно нужно и скоростные характеристики не ухудшать, как минимум. Эта проблема даже в настольных системах проявляется, где больше двух-трех модулей на канал не используется. Например, может быть так: один модуль — DDR3 1333, два — DDR3 1066, три — DDR3 800. Очень много медленной памяти, конечно, иногда лучше, чем мало быстрой, но идти на такие издержки все равно нежелательно. А иногда и невозможно.

Над проблемой увеличения количества поддерживаемых одним каналом контроллера модулей памяти в Intel работали долго и небезуспешно. Однако оказалось, что конечный результат (FB-DIMM) изначально поставленным требованиям удовлетворяет, но его использование вызывает массу нежелательных побочных эффектов.

Остается только один путь — во-первых, перенести контроллер памяти в процессор, что в многопроцессорной системе автоматически обеспечивает нам поддержку и нескольких контроллеров памяти. Во-вторых, увеличивать количество каналов памяти. И то, и другое было сделано. Результат? В системе на двух Xeon, равно как и в системе на двух Opteron, есть два контроллера памяти. Только в первой оба трехканальные, а во второй — двухканальные, что дает нам шесть и четыре канала памяти, соответственно. При установке двух модулей памяти на канал (очень даже щадящий режим) в первой системе их окажется 12, а во второй — 8. Допустим, каждый модуль имеет емкость 4 ГБ, тогда в первой системе окажется 48 ГБ, а во второй — 32 ГБ. В ряде задач это сразу обеспечит первой системе весомое преимущество. А как в сервере на Оптеронах теми же модулями «добить» память до 48 ГБ? Легко — устанавливаем три модуля на канал и… вся система памяти начинает работать медленнее, поскольку, например, задержки придется сильно увеличить. И получается: при одинаковой скорости работы памяти система «и» имеет в полтора раза больший ее объем, чем система «а», а при равном объеме система «и» работает с памятью быстрее, чем система «а».

Именно поэтому в Xeon трехканальный контроллер памяти нужен. Он и в Opteron нужен, но не удалось в свое время сделать. Точно так же, как сейчас Intel не удалось четыре канала реализовать. Все равно по этому пути идти обоим производителям, поскольку альтернативным (а именно FB-DIMM и количество модулей на канале увеличивать) один из них уже идти пробовал и остался не очень довольным.

А зачем все это в зоопарке, на рабочем столе обычного пользователя? Правильно — незачем. Кому нужно — те многопроцессорную рабочую станцию купят и сведут задачу к предыдущей. Основная масса как-то желанием не горела и по 8 ГБ в компьютеры устанавливать (хотя это-то давно доступно), так что ей нет разницы — можно поставить 12 или как. Тем более что сейчас уже при двух модулях на канал двухканального контроллера памяти можно получить и 16 ГБ, а вопрос — насколько это хуже/лучше, чем 24 ГБ, для нормального пользователя компьютера сродни вопросу, сколько ангелов поместятся на кончике иглы.

Итого

При взгляде на итоговую диаграмму, возникает закономерный вопрос — а зачем мы всем этим занимались? Ведь видно, что к финишу практически все пришли одновременно. Гипотетический одноканальный режим свою относительную бессмысленность показал, двухканальный — как и можно было предположить из тестов в синтетике, оказался самым быстрым. Разброс в 2% между лучшим и худшим случаями на таком представительном количестве приложений — очень хороший результат. Показывает, что, как бы то ни было, но в основном наша текущая методика тестирования продолжает оставаться методикой тестирования процессоров, и на общий итоговый балл прочие характеристики системы влияют весьма слабо.

Но! Успокаиваться на этом рано — как мы видим, в общем зачете получилась идиллия именно из-за того, что разные приложения друг друга уравновешивают, однако ведут себя они совершенно по-разному. Кому-то нужно много памяти, кому-то ее увеличение наоборот — мешает, кому-то не важен объем, но жизненно важны низкие задержки, но DivX, по сути, «презрел» все объективно существующие параметры памяти и отдал предпочтение трехканальному режиму в любом виде. Поэтому, при сравнении систем с разными конфигурациями памяти в рамках одной статьи (или самостоятельно), в конкретных тестах не стоит забывать поинтересоваться — как именно получен тот или иной результат. Впрочем, не так уж долго осталось нам возиться именно с разными конфигурациями — LGA1156, напомним, поддерживает только два канала памяти, так что с этими процессорами все будет просто и логично. Устройства в конструктиве LGA1366 мы продолжим тестировать в конфигурации 3х2, однако иногда будем извлекать из запасников и 2х2 (когда нежелательно будет делать поправки в уме на особенности системы памяти). Можно было бы даже полностью перейти на последние, но нет смысла — в среднем, они, конечно, несколько быстрее, но поддержка трех каналов памяти эксклюзивная особенность LGA1366, так что пусть за нее отдувается. Нам просто достаточно помнить, что трехканальный доступ к памяти на этой платформе производительность совсем не увеличивает, а даже наоборот.

Контроллер памяти: структура и синхронизация

Введение

Много ли вы слышали о контроллере памяти? Возможно, вы когда-то пытались найти информацию о контроллере памяти, но толком ничего не находили. Даже в книгах, к сожалению, есть только небольшие упоминания. Получается, что все знают про то, что контроллер памяти существуют, но никто не имеет представление, что это такое (именно на таких читателей рассчитана данная статья). Мне повезло наткнуться на статьи инженеров, которые решают проблемы проектирования и синхронизации контроллеров памяти в своих проектах. Эту информацию мы используем, чтобы понять, как устроен и как работает КП на высоком уровне.

Для самых маленьких

реклама

Процессору необходимо обращаться в память, как для получения инструкций, так и для данных, требуемых при исполнении инструкций. В качестве памяти может служить и основная оперативная память. Здесь появляется контроллер памяти, обрабатывающий запросы процессора. В общем-то о его предназначении вы узнаете, если прочитаете статью полностью.

Как устроена память

Во-первых, разберёмся с тем, как устроена память в принципе. Вы наверняка знаете, что у плашки оперативной памяти есть чипы памяти. Характеристика «плотность чипов» как раз обозначает объём в чипе памяти. Всё просто. Если есть чипы, емкость которых по 8 гигабит каждая (по одному гигабайту каждая), то 8 таких в сумме дадут 8 гигабайт (64 гигабит), поэтому мы и скажем, что это плашка на 8гб. Сам чип состоит из нескольких банок, а в свою очередь банки состоят из совокупности ячеек. Объём всех ячеек в чипе памяти одинаковый, причем ячейка по объёму не обязательно равна одному биту.

реклама

Важно сказать, что в реальности данные и адреса не направлены в разные стороны. Это единая шина, у которой линии разделены соответственно на информационные (D) и адресные (A) линии. А могут быть не разделены, если применяется мультипелксная шина. В такой реализации и адреса, и данные передаются по одним и тем же линиям последовательно. Это может решить проблему расфазировки шины (когда данные приходят быстрее адреса), но мультиплекс будет медленнее. Помимо всего прочего в статье И.А Петрова упоминается DDR4 3DS, использующая стеки чипов (друг на друга кладутся), которые взаимодействуют через связь сквозь кремний (through silicon via, TSV). Один такой чип в стеке называется логическим ранком. Логической страницей называется матрица внутри банка.

Механизм интерливинга и конвейерная шина памяти

Теперь разбираемся с механизмом интерливинга. Из статьи И.А Петрова: «В каждом логическом банке (размером от 256 Мбайт до 2 Гбайт) можно одновременно задействовать лишь одну страницу памяти (8 Кбайт). Переход к другой странице в рамках одного логического банка возможен через 45–50 нс». Далее написано, что механизм интерливинга, то есть перемешивание страниц памяти, находящихся в других банках памяти, избавляет от этой проблемы. Сначала непонятно каким образом, но это действительно так. Оказывается, банки для того и были введены, чтобы осуществлять несколько параллельных запросов к ним. Это так называемая конвейерная архитектура шины памяти. Если вы знакомы с конвейерной архитектурой ядер процессора, тогда вы примерно понимаете насколько круто, что у памяти такая тоже есть.

реклама

Здесь CK — это линия, по которой идут импульсы от тактового генератора с определенной частотой. Можно сказать, что шина работает на частоте CK или синхронизируется по CK. Как мы видим, циклом шины является период от фронта (переход от логического 0 к 1, поднятие по импульсу) синхросигнала до фронта следующего синхросигнала. Группа управляющих линий обозначена CMD, адресных — ADDR, а информационных — DATA.

Запрос к памяти состоит из трёх этапов:

1) Открытие строки для подготовки к обращениям (ACT).

2) Обращение к отдельным словам строки или к нескольким словам при использовании пакетного режима (длина пакета фиксирована).

3) Закрытие строки (PRECHARGE) и подготовка к следующей активизации.

В нашем примере важно, чтобы фаза активизации (ACT) предшествовала фазе READ (или WRITE) на 2 цикла (обязательно смотрите на рисунок). Также известно, что данные готовы на следующем цикле после фазы READ (WRITE), а PRECHARGE происходит минимум на два цикла позже фазы READ (WRITE). Данные обязательные условия называются протоколом. Все операции занимают определенное число циклов шины, поэтому известно, когда получать данные, когда открывать и закрывать строку. Конвейерный режим нужен, чтобы исключить простои. Ещё раз смотрите на рисунок: без конвейерного режима на цикле 1 образовался бы пустой цикл. Вместо простоя происходит активизация строки из другого банка. Преимущества очевидны.

Структура контроллера памяти

реклама

Это КП планировшегося Эльбруса 16CB. В контроллерах памяти есть буферы записи и чтения (в нашем примере этот буфер расположен за пределами КП). Когда КП получает данные от основной ОЗУ, данные сначала помещаются в буфер чтения. Аналогично с записью: данные от ядер поступают в буфер записи. Буферы выступают в роли промежуточной памяти для хранения, так как удобно получать данные большего объёма. Ведь ядру, которому понадобились данные по адресу A, с большой вероятностью понадобятся данные по адресу A+1. Это так называемый принцип локальности, на нем также основывается принцип кэширования. Буфер записи в свою очередь реализует отложенную запись.

В реестре запросов, как ни странно, хранятся запросы обращения к основной памяти. Каждая ячейка реестра включает в себя адрес, тип операции, признак готовности данных для записи, возраст запроса и стадию обработки запроса.

Планировщик занимается тем, что выбирает порядок запросов так, чтобы сократить среднее время на обработку одной заявки. Как это достигается? С помощью последовательно соединенных фильтров планировщика. На выходе планировщика расположен блок формирования операций для шины памяти, в котором запросы полностью перекрываются (отсутствуют пустые циклы на шине, что уже было описано выше).

В Эльбрус 16CB фильтры соединены в таком порядке:

фильтр ресурсов, задерживающий запросы, выполнение которых невозможно вследствие недостаточности объемов буферов чтения или записи

фильтр адресной зависимости, обеспечивающий корректную последовательность обращений в случае обращений по одному адресу (запросу по одному адресу должны выполняться последовательно. Представим ситуацию, что в реестр поступает запрос на запись данных в оперативную память на адрес A, а следующий запрос — чтение данных по адресу A. Без этого фильтра, так как чтение имеет более высокий приоритет над записью, считались бы устаревшие данные)

фильтр приоритета выполнения запроса в открытую страницу логического банка, исключающий дополнительные операции открытия страниц (ACT). Запрос отсеивается, если он попадает в закрытую страницу, хотя в то же время есть запросы, адресованные в открытую страницу. Данный фильтр минимизирует команды активизации, что и уменьшит среднее время обработки заявки в реестре.

фильтр на приоритет операций чтения. Чтение гораздо важнее записи для производительности, поэтому у планировщика в приоритете запросы чтения

фильтр протокольных блокировок, задерживающий запросы, нарушающий протокол (об этом было раньше и ещё будет позже)

фильтр возраста. Выбирается самый старший запрос, то есть, который вошёл раньше всех в реестр.

О фильтрах почти полностью скопировано со статьи И.А Петрова, но кое-где добавлены собственные пояснения. Ниже приложен схематичный рисунок планировщика

Теперь про протокольные блокировки. Когда мы говорили о конвейерной шине памяти, я написал, что есть некий протокол. Его необходимо соблюдать для каждого банка памяти с помощью счетчиков-таймеров внутри контроллера протокольных блокировок. Из книги Танебаума: «Как Core i7 узнает, когда следует ожидать возвращения данных команды READ и когда можно выдавать новый запрос к памяти? Для этого он осуществляет полное моделирование внутренней деятельности каждой подключенной микросхемы DDR3. Соответственно он ожидает возвращения данных в правильно выбранном цикле и знает, что операцию предзаряда не следует начинать раньше чем через два цикла после последней операции чтения. Core i7 может прогнозировать все эти события, потому что интерфейс памяти DDR3 работает синхронно, так что все операции занимают четко определенное количество тактов шины DDR3.»

Моделированием внутренней деятельности как раз занимается контроллер блокировок. Фильтр протокольных блокировок в планировщике использует это и отсеивает невозможные запросы. Основой динамической памяти (любая SDRAM DDR относится к динамической памяти) является конденсатор. Конденсатор может хранить заряд в течении короткого времени, иными словами может служить битом памяти. Ведь у бита, как и у конденсатора, есть два состояния. У конденсатора либо есть заряд (бит 1, логический 1), либо его нет (бит 0, логический 0). При считывании конденсатор разряжается, и если заряд был, то значение однобитной ячейки равно единице, и это значение мы можем использовать. Также после считывания нужно заряжать конденсатор заново, если заряд был (другими словами: значение однобитной ячейки должно быть равно одному, если её значение было равно одному до разрядки). Контроллер регенерации памяти как раз занимается тем, что выдает команды регенерации памяти.

Обычно для реализации многоканального режима работы устанавливают несколько рассмотренных нами одноканальных контроллеров памяти. Как, например, двухканальный контроллер памяти Эльбруса S2 включает по сути два отдельных контроллера памяти, находящиеся в одном блоке.

Синхронизация подсистемы памяти

В подсистеме памяти чаще всего различают три частотных домена: системный домен, домен контроллера памяти и домен самой памяти. Пример представлен ниже.

Решение проблемы синхронизации включает в себя следующие вопросы: какие тактовые частоты будут у доменов и каким образом они будут взаимодействовать в совокупности. От этого будет зависеть задержка обращения в память и максимально допустимая частота памяти, ведь частота контроллера памяти может её ограничить. Итак, синхронизация подсистемы памяти влияет на её эффективность.

Для начала рассмотрим проблему метастабильности на примере триггеров. Что такое триггеры? Это защелки, которые синхронизируются на фронте или спаде тактового импульса. Много непонятных слов? О том, как работают защелки знать не обязательно. Достаточно понимать, что защелка может хранить один бит информации. Но синхронная защелка может записать бит информации только тогда, когда на одном из входов защелки есть тактовый импульс. Таким образом, тактовый импульс является своего рода сигналом, что данные с входа данных можно записать. А триггер отличается тем, что ему нужен не весь тактовый импульс, а только его фронт или спад.

В нашем случае триггеры будут синхронизироваться по фронтам, так что далее рассматривать будем только фронт, но помним, что для спада всё то же самое.

Для правильной работы триггера необходимо, чтобы входные данные триггера некоторое время оставались неизменны до фронта импульса. Этот временной интервал называется Time Setup (Ts). Аналогично после фронта импульса данные также некоторое время должны оставаться неизменными, и это временное требование называется Time Hold (Th).

Если требования для входных данных выполняются, то на выходе триггера данные также появляются. А иначе верное выходное значение триггера устанавливается через большее время. Такое состояние называется метастабильностью. В метастабильном состоянии сигнал пребывает в состоянии, которое нельзя назвать ни логическим нулём, ни логической единицей. Дальнейшее распространение метастабильного сигнала может привести к сбою всей системы.

Данная проблема характерна для передачи данных между доменами с разными частотами. Вы узнаете почему позже, а пока просто покажу частоты доменов подсистемы памяти в разных проектах.

Эльбрус-С+:

системный домен с частотой 500 МГц (системная частота);

домен оперативной памяти, частота которого относится к системной как 4/5, 2/3, 3/5 или 1/2;

домен ядра контроллера оперативной памяти, отношение его частоты к частоте памяти равно 1/2.

Один из КП А.С Кожина:

Системный домен (System domain) – 800/1000 МГц

Домен оперативной памяти (DDR domain) – 800, 666, 533, 400 МГц

Домен ядра контроллера (MC domain) – частота в 2 раза ниже частоты памяти

Домен оперативной памяти ровно в два раза меньше эффективной частоты оперативной памяти.

В двух случаях мы наблюдаем подсистему памяти, частотные домены которой имеют разные частоты (логично).

Возвращаемся к проблеме метастабильности. На рисунке (а) мы видим, что фронт CLKB захватывает нестабильный сигнал DA. Временной интервал между фронтами оказался недостаточным. В итоге мы имеем метастабильный сигнал DB.

Одними из решений данной проблемы является добавление ещё одного триггера. Совокупность триггеров на приемной стороне образует синхронизатор (рисунок б). Дополнительный триггер помог избавиться от дальнейшего распространения метастабильности сигналов, ведь DB2 принимает правильное значение. Однако не всегда такой синхронизатор решает проблему метастабильности. Например, здесь.

В первом случае CLKB не успевает захватить сигнал данных DA, а во втором случае CLKB захватывает DA три раза, то есть по сути одиночную посылку воспринимает, как множество посылок. В первом случае наблюдается передача из высокочастного домена в низкочастотный домен, а во втором — из низкочастотного в высокочастотный. Рассмотрим другой метод.

W_ADR соответствует значению Write Pointer, R_ADR соответствует значению Write Read.

Так как буфер асинхронный, то и write control logic, и read control logic функционируют на разных частотных доменах (имеют разные частоты).

Блок Flag Logic служит для формирования информационных сигналов о заполнении. Ниже представлена та же схема на более низком уровне.

Сначала указатель записи формируется в модуле в GRAYCOUNTER в коде Грея. Код Грея характерен тем, что в последовательности предыдущее значение от данного отличается только одним битом.

То есть в двоичной системе счисления будет так:

000

001 (отличается от предыдущего(000) одним битом)

010 (отличается от предыдущего(001) уже двумя битами в двух позициях)

011

100 (а здесь данное слово отличается всеми тремя битами от предыдущего)

101

110

111

Тогда как в коде Грея это будет выглядеть вот так:

000

001

011

010

110

111

101

100

Если мы возьмем любое значение, то опять же увидим, что оно отличается от предыдущего и от следующего только одним битом в какой-либо позиции. А зачем он нужен здесь вы узнаете совсем скоро. Далее из GRAYCOUNTER данные указателя отправляются в приемник через шину wrptr_g, а приемник работает на другой частоте. Здесь под шиной мы понимаем только совокупность проводников, по которым идет по биту информации. Но для исключения метастабильности на этом этапе к каждой линии шины подведен дополнительный триггер на передающей стороне, на рисунке он также изображен, и три триггера на принимающей стороне (на рисунке синхронизатор). Тогда возможно такое (при изменении указателя записи, то есть данных в GRAYCOUNTER), что сигналы на линиях шины будут задержаны относительно друг-друга, а это приведет к тому, что в одних линиях приемник захватит новые значения, а в других — старые. А в коде Грея новое значение отличается всего на один бит. У нас будет всего два варианта: либо старое (пусть будет 011), либо новое значение (пусть будет 010). А это к сбою работы FIFO-буфера не приведет. Далее gray2bin модуль сможет преобразовать код Грея в двоичное число. Также в любом FIFO-буфере с помощью сравнений указателей записи и чтения, узнается пуст ли или полон буфер. Верхняя граница известна, а при равенстве указателей мы понимаем, что буфер пуст. Ведь нельзя считать пустотой буфер или записать данные в переполненный, так что устанавливаются флаги из Flag Logic.

Асинхронные FIFO-буферы используются очень часто из-за того, что они могут передать данные доменов с очень разным соотношением частот. Да и вообще это очень удобно, ведь можно их заказывать готовые. Но, к сожалению, задержки будут гораздо больше: прохождение сигналов через триггеры, преобразование в код Грея и обратно — это довольно долго.

Ещё один интересный метод пересинхронизации я вычитал из статьи А.С Кожина, какую я укажу в источниках. Этот метод использовался в Эльбрус-C+, он предусматривает метки (сигналы) для высокочастотного домена. Причем для входа высокочастотного домена предусматривается метка clabel_i, служащая для того, чтобы высокочастотный домен не воспринимал одну посылку, как несколько (об этом было сказано, когда мы рассматривали синхронизаторы). Для выхода высокочастотного домена используется метка clabel_o, гарантирующая, что низкочастотный приемник примет данные (об этом тоже было сказано).

Здесь метка clabel_o разрешает изменение данных на выходе триггеров со стороны высокочастотного домена (обращайте внимание на data_out). На следующем фронте импульса приемника (приемник работает на частоте 2/5 Fsys), данные захватываются (это второй импульс 2/5 Fsys. Соотнесите его с data_out). Таким образом выполняется передача данных из высокочастотного домена в низкочастотный.

Здесь важно правильно формировать метки, чтобы соблюдались следующие требования: новые данные на data_out не должны захватываться предыдущим фронтом импульса (если бы первый импульс 2/5 Fsys захватил данные вместо второго), новые данные должны успеть переключиться до следующего фронта импульса (такое произошло, если бы второй импульс cabel_o появился позже).

Всё аналогично при передаче из низкочастотного домена в высокочастотный. Только в этому случае метка cabel_i обеспечивает выбор только одного фронта высокой частоты. Метки формируются в специальном блоке формирования меток.

Он состоит из регистра (такая память, состоящая из триггеров). Значение в регистре определяет, в какие такты периода биений (T align) разрешено выдавать метку. Период биений здесь, как вы можете посмотреть на предыдущем рисунке с меткой cabel_o — это период, при котором совпадают фронты импульсов. Ширина регистра определяется количеством тактовых импульсов за период биений (в Fsys было 5 таких). Основная метка выдается на частоте большего домена. Сигнал mode задает режим работы блоку формирования в зависимости от частот передающего и принимающего доменов. Указатель (Pointer) указывает на значение регистра, отвечающее за состояние метки (будет ли выдана или нет). Сигнал beat — это комбинационный сигнал биений, который определяет начало периода биений. Он помогает восстановить правильное значение указателя, если в нем изменился разряд.

Также синхронизация невозможна без самого блока пересинхронизации. Здесь всё стандартно, но всё-таки требуется раскрыть передачу из одного домена в другой, когда частоты доменов близки. Близкими частоты будут, если на низкочастотный импульс приходится один фронт высокочастотного домена или f1/f2 f2). Прием/передача могут быть невозможны из-за несоблюдения временнЫх интервалов. В этом случае используются триггеры, задерживающие на половину такта данные, и дополнительная метка, определяющая, когда задержанные данные можно использовать.

Подобный метод пересихронизации не так удобен и универсален, как асинхронный FIFO-буфер, но зато имеет меньшие задержки.

На этом всё. Спасибо за внимание, критикуйте, обсуждайте и задавайте вопросы.

Источники

Архитектура компьютера, 6-ое издание, Э. Танебаум и Т. Остин (Отсюда я взял про триггеры и прочее на цифровом логическом уровне, устройство памяти и шины)

Контроллер памяти DDR2 SDRAM и его система синхронизации в составе системы на кристалле «Эльбрус-S2», А. С. Кожин (по факту источник-пустышка, отсюда впервые услышал про метки, но взял только картинку с кп)

Метастабильность триггера и межтактовая синхронизация, «nerudo» (статья с хабра. Взял отсюда картинку, где Ts и Th интервалы)

Одно- и двухпортовая память. FIFO-буфер. Проблемы метастабильности, юутб-канал «Электроника и наноэлектроника» (типо лекция, мне показалась она достаточно сомнительной, но разобраться действительно помогла)

Что такое кэш процессора, и как он работает, Сергей Пахомов (здесь было про промежуточную память)

Флэш-память на любой вкус, Сергей Пахомов (про регенерацию памяти на уровне конденсаторов)